IBM RS64

Este artículo incluye una lista de referencias generales , pero carece de suficientes citas en línea correspondientes . ( Marzo de 2014 ) |

| POWER, PowerPC, and Power ISA architectures |

|---|

| NXP (formerly Freescale and Motorola) |

| IBM |

|

| IBM/Nintendo |

| Other |

| Related links |

| Cancelled in gray, historic in italic |

IBM RS64 es una familia de microprocesadores introducida a mediados de la década de 1990 y utilizada en los servidores RS/6000 y AS/400 de IBM .

Estos microprocesadores implementan la arquitectura de conjunto de instrucciones (ISA) "Amazon" o "PowerPC-AS" . Amazon es un superconjunto del conjunto de instrucciones PowerPC , con la adición de características especiales que no están en la especificación PowerPC, derivadas principalmente de POWER2 [ cita requerida ] y el procesador AS/400 original, y ha sido de 64 bits desde el principio. Los procesadores de esta familia están optimizados para cargas de trabajo comerciales ( rendimiento de números enteros , cachés grandes, bifurcaciones frecuentes ) y no presentan el fuerte rendimiento de punto flotante de los procesadores de la familia POWER , su hermano.

La familia RS64 se eliminó poco después de la introducción del POWER4 , que se desarrolló para unir las familias RS64 y POWER.

Historia

En 1990, el equipo de ingeniería AS/400 en IBM Rochester comenzó a trabajar en una nueva arquitectura conocida como C-RISC (Commercial RISC ) para reemplazar la arquitectura IMPI del AS/400. [1] [2] C-RISC fue una evolución del conjunto de instrucciones IMPI, extendiendo el espacio de direcciones a 96 bits y agregando algunas instrucciones RISC para acelerar las aplicaciones comerciales más intensivas en computación que se estaban creando para los AS/400. El presidente de IBM, Jack Kuehler, quería que usaran PowerPC, pero se resistieron, argumentando que el conjunto de instrucciones PowerPC de 32/64 bits existente no permitiría una transición viable para el software OS/400 y que el conjunto de instrucciones existente requería extensiones para las aplicaciones comerciales en el AS/400. Ante la insistencia de Kuehler, un equipo en Rochester dirigido por Frank Soltis investigó la viabilidad de extender el conjunto de instrucciones PowerPC para soportar las necesidades de la plataforma AS/400. Estas extensiones se conocieron como Amazon y fueron seleccionadas por la gerencia ejecutiva de IBM para un mayor desarrollo durante el desarrollo continuo de C-RISC. [3]

Al mismo tiempo, los desarrolladores del RS/6000 estaban ampliando ampliamente su línea de productos para incluir sistemas que abarcaban desde estaciones de trabajo de gama baja , pasando por sistemas SMP de gran empresa que competían con mainframes , hasta sistemas de supercomputación en clúster RS/6000-SP2 . Los procesadores PowerPC desarrollados en la alianza AIM se adaptaban bien a las estaciones de trabajo RISC de gama baja y a los pequeños espacios de servidor. Pero los mainframes y los grandes sistemas de supercomputación en clúster requerían más prestaciones y fiabilidad, disponibilidad y capacidad de servicio que los procesadores diseñados para los Apple Power Macs . Se necesitaban múltiples diseños de procesadores para satisfacer simultáneamente los requisitos de los Apple Power Mac centrados en los costes, los sistemas RS/6000 de alto rendimiento y RAS, y la transición de AS/400 a PowerPC.

Amazon se amplió para soportar también esas características, de modo que los procesadores pudieran diseñarse para usarse en máquinas RS/6000 y AS/400 de alta gama.

El proyecto para desarrollar el primer procesador de este tipo fue "Bellatrix" (el nombre de una estrella en la constelación de Orión , también llamada "Estrella del Amazonas"). El proyecto Bellatrix era extremadamente ambicioso en su uso generalizado de circuitos basados en pulsos y con temporizador automático y las herramientas EDA requeridas para apoyar esta estrategia de diseño, y finalmente fue cancelado. Para abordar los mercados de estaciones de trabajo técnicas, supercomputadoras y de ingeniería/ciencia, IBM Austin (la casa de los RS/6000) comenzó entonces a desarrollar una versión de un solo chip del Power2 (P2SC) de rápida comercialización en paralelo con el desarrollo de un sofisticado procesador PowerPC de 64 bits con las extensiones POWER2 y dos sofisticadas unidades de punto flotante MAF (el POWER3/630). Para abordar las aplicaciones comerciales RS/6000 y los sistemas AS/400, IBM Rochester (la cuna de los AS/400) comenzó a desarrollar el primero de los procesadores PowerPC de 64 bits de gama alta con extensiones AS/400, e IBM Endicott comenzó a desarrollar un procesador PowerPC de un solo chip de gama baja con extensiones AS/400.

Cobra y muskie

En 1995, IBM lanzó el procesador Cobra , o A10 , la primera implementación completa de PowerPC AS, para los sistemas IBM AS/400 . Era un procesador de un solo chip que funcionaba a 50-77 MHz. Fue diseñado con una metodología semipersonalizada, como consecuencia de las limitaciones de tiempo de comercialización. La matriz contiene 4,7 millones de transistores y mide 14,6 mm por 14,6 mm (213 mm 2 ). Fue fabricado por IBM en su proceso CMOS 5L, un proceso CMOS de cuatro capas de metal de 0,5 μm . Utilizaba una fuente de alimentación de 3,0 V y disipaba 17,7 W como máximo y 13,4 W como mínimo a 77 MHz. Estaba empaquetado en una matriz de rejilla de bolas de cerámica (CBGA) de 625 contactos que medía 32 mm por 32 mm.

Cobra fue precedido por una implementación simplificada conocida como Cobra-Lite en 1994, que se utilizó en los primeros sistemas IBM Advanced/36 . [1] Carecía de 17 instrucciones del PowerPC AS ISA completo que no eran necesarias para el Advanced/36.

En 1996, IBM lanzó la versión de gama alta, multichip, SMP de 4 vías, denominada Muskie , A25 o A30, en sistemas AS/400. Funcionaba a 125-154 MHz y se fabricaba mediante un proceso de fabricación BiCMOS .

Estos procesadores sólo se utilizaron en máquinas AS/400 y Advanced/36.

RS64

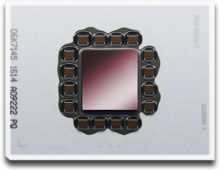

El RS64 o Apache se introdujo en 1997. Fue desarrollado a partir de "Cobra" y "Muskie", pero incluía una ISA PowerPC más completa y, por lo tanto, estaba destinado a utilizarse en máquinas RS/6000 , así como en sistemas AS/400. Presentaba un caché L1 en chip de 128 KB en total , 4 MB de caché L2 fuera del chip a máxima velocidad en un bus de 128 bits y una frecuencia de reloj de 125 MHz. Se escaló a una configuración SMP de 12 procesadores en las máquinas de IBM.

El RS64 se llamaba A35 en AS/400 y en un tiempo se lo conocía como PowerPC 625 , entre el extinto PowerPC 620 y el PowerPC 630 (más tarde rebautizado como POWER3 ).

Fue fabricado con un proceso de fabricación BiCMOS.

RS64-II

El RS64-II o Northstar se introdujo a 262 MHz en 1998 con 8 MB de L2 de velocidad completa en un bus 6XX de 256 bits (también utilizado en PowerPC 620 y POWER3 ). Las placas de procesador que contenían 4 RS64-II se podían intercambiar en máquinas diseñadas para placas RS64 de 4 vías similares, evitando una "actualización de carretilla elevadora". El RS64-II contenía 12,5 millones de transistores, tenía 162 mm² de tamaño y consumía 27 vatios de potencia máxima. La fabricación cambió a una fabricación CMOS de 0,35 μm .

El RS64-II fue el primer procesador de mercado masivo que implementó el multithreading . Básicamente, cada chip almacena información de estado para 2 subprocesos en un momento dado y parece ser dos procesadores para el SO. Un procesador lógico ejecuta lo que se llama el subproceso en primer plano. Cuando este subproceso encuentra un evento de alta latencia ( error de caché L2 , etc.), el subproceso en segundo plano se cambia al segundo procesador lógico desde el punto de vista del SO. En el caso de un evento de latencia "menos larga" (error de L1, etc.), el cambio de subproceso solo se producirá si el subproceso en segundo plano está listo para ejecutarse. Si el subproceso en segundo plano también está esperando un error, el cambio de subproceso no se producirá. IBM llama a este esquema "multithreading de grano grueso". No es exactamente lo mismo que el multithreading simultáneo que se encuentra en los procesadores Pentium 4 posteriores . Un documento de IBM señala que el esquema de grano grueso se adapta mejor a una microarquitectura en orden como RS64.

RS64-II se llamó A50 en los sistemas AS/400.

RS64-III

El RS64-III o Pulsar se introdujo en 1999 a 450 MHz. Entre los cambios clave se incluyen cachés de datos e instrucciones L1 más grandes de 128 KiB, una precisión mejorada en la predicción de saltos y una reducción de las penalizaciones por errores de predicción de saltos de cero o un ciclo. El RS64-III tiene una secuencia de cinco etapas y un bus de caché L2 de 256 bits de ancho, que proporcionaba al procesador 14,4 GB/s de ancho de banda desde el caché L2 de 8 MiB, implementado con SRAM DDR de 225 MHz.

El RS64-III tiene 34 millones de transistores, un tamaño de matriz de 140 mm² y está fabricado mediante el proceso CMOS 7S de 0,22 μm con seis niveles de interconexión de cobre .

En el año 2000, IBM lanzó una versión refinada llamada IStar , fabricada con un proceso de fabricación SOI con interconexiones de cobre, que aumentó la frecuencia de reloj del procesador a 600 MHz. Este fue el primer procesador implementado con este proceso. Sin embargo, arquitectónicamente el IStar era idéntico al Pulsar.

RS64-IV

El RS64-IV o Sstar se introdujo en el año 2000 a 600 MHz y más tarde se amplió a 750 MHz. Se admitían hasta 16 MB de caché DDR L2 de la misma manera que el RS64-III (ancho de banda de 19,2 GB/s). El RS64-IV tenía 44 millones de transistores y tenía un tamaño de 128 mm² fabricado con un proceso de 0,18 μm. A diferencia del POWER, el consumo de energía se mantuvo bajo, por debajo de los 15 vatios por núcleo.

Durante un tiempo, mientras la línea POWER se estancaba a la mitad de la velocidad de reloj de sus competidores, la familia RS64 se situaba en lo más alto de la línea de servidores UNIX SMP de gran tamaño de IBM . El rendimiento de carga de trabajo entera/comercial del RS-64 IV era similar al de los procesadores Sun Microsystems con los que competía, aunque su potencia de coma flotante no era comparable a la del POWER3-II contemporáneo , que siguió siendo razonablemente competitivo a lo largo de su ciclo de vida.

Referencias

- ^ de Frank G. Soltis (1997). Inside the AS/400, segunda edición. Duke Press. ISBN 978-1882419661.

- ^ Leif Svalgaard (8 de octubre de 2003). "Re: Re: emulador MI". MI400 (lista de correo) . Consultado el 26 de febrero de 2021 .

- ^ Adam T. Stallman; Frank G. Soltis (1 de julio de 1995). "Inside the PowerPC AS". Revista System iNEWS . Archivado desde el original el 31 de agosto de 2013.

Lectura adicional

- Gwennap, Linley (31 de julio de 1995). "IBM crea procesadores PowerPC para AS/400". Microprocessor Report .

Enlaces externos

- Documento de IBM sobre RS64-IV

- 27 años de IBM RISC

- ¿Cuándo PowerPC no es PowerPC? - Historia de la arquitectura POWER por Frank Soltis

- PODER al pueblo

- Diseño de procesador comercial compatible con PowerPC de 64 bits de cuarta generación

- Dentro del PowerPC AS Archivado el 31 de agosto de 2013 en Wayback Machine