CUDA

Este artículo tiene varios problemas. Ayúdenos a mejorarlo o a discutir estos problemas en la página de discusión . ( Aprenda cómo y cuándo eliminar estos mensajes )

|

| |

| Desarrollador(es) | Nvidia |

|---|---|

| Lanzamiento inicial | 23 de junio de 2007 ( 23 de junio de 2007 ) |

| Versión estable | 12.6 / agosto 2024 ( 2024-08 ) |

| Sistema operativo | Ventanas , Linux |

| Plataforma | GPU compatibles |

| Tipo | GPGPU |

| Licencia | Propiedad |

| Sitio web | desarrollador.nvidia.com/cuda-zone |

En informática , CUDA (originalmente Compute Unified Device Architecture ) es una plataforma de computación paralela y una interfaz de programación de aplicaciones (API) propietaria [1] que permite al software utilizar ciertos tipos de unidades de procesamiento gráfico (GPU) para un procesamiento acelerado de propósito general, un enfoque llamado computación de propósito general en GPU ( GPGPU ). API de CUDA y su tiempo de ejecución: La API de CUDA es una extensión del lenguaje de programación C que agrega la capacidad de especificar paralelismo a nivel de subproceso en C y también especificar operaciones específicas del dispositivo GPU (como mover datos entre la CPU y la GPU). [2] CUDA es una capa de software que brinda acceso directo al conjunto de instrucciones virtuales de la GPU y a los elementos computacionales paralelos para la ejecución de núcleos de cómputo . [3] Además de los controladores y los núcleos de tiempo de ejecución, la plataforma CUDA incluye compiladores, bibliotecas y herramientas para desarrolladores para ayudar a los programadores a acelerar sus aplicaciones.

CUDA está diseñado para funcionar con lenguajes de programación como C , C++ , Fortran y Python . Esta accesibilidad facilita a los especialistas en programación paralela el uso de los recursos de la GPU, a diferencia de las API anteriores como Direct3D y OpenGL , que requerían habilidades avanzadas en programación de gráficos. [4] Las GPU impulsadas por CUDA también admiten marcos de programación como OpenMP , OpenACC y OpenCL . [5] [3]

CUDA fue creado por Nvidia en 2006. [6] Cuando se introdujo por primera vez, el nombre era un acrónimo de Compute Unified Device Architecture, [7] pero luego Nvidia abandonó el uso común del acrónimo y ahora rara vez lo expande. [8]

Fondo

La unidad de procesamiento gráfico (GPU), como procesador informático especializado, atiende las demandas de tareas de procesamiento intensivo de gráficos 3D de alta resolución en tiempo real . En 2012, las GPU habían evolucionado hasta convertirse en sistemas multinúcleo altamente paralelos que permiten la manipulación eficiente de grandes bloques de datos. Este diseño es más eficaz que las unidades centrales de procesamiento (CPU) de propósito general para algoritmos en situaciones en las que el procesamiento de grandes bloques de datos se realiza en paralelo, como:

- funciones hash criptográficas

- aprendizaje automático

- simulaciones de dinámica molecular

- motores de fisica

Ian Buck, mientras estaba en Stanford en 2000, creó una plataforma de juegos 8K usando 32 tarjetas GeForce, luego obtuvo una subvención de DARPA para realizar programación paralela de propósito general en GPU . Luego se unió a Nvidia, donde desde 2004 ha estado supervisando el desarrollo de CUDA. Al impulsar CUDA, Jensen Huang apuntó a que las GPU de Nvidia se convirtieran en un hardware general para la computación científica. CUDA se lanzó en 2006. Alrededor de 2015, el enfoque de CUDA cambió a redes neuronales. [9]

Ontología

La siguiente tabla ofrece una descripción no exacta de la ontología del marco CUDA.

| memoria (hardware) | memoria (código o alcance de variable ) | computación (hardware) | cálculo (sintaxis del código) | computación (semántica del código) |

|---|---|---|---|---|

| RAM | variables no CUDA | anfitrión | programa | una llamada de rutina |

| VRAM , caché L2 de GPU | global, constante, textura | dispositivo | red | Llamada simultánea de la misma subrutina en muchos procesadores |

| Caché L1 de la GPU | local, compartido | SM ("multiprocesador de transmisión") | bloquear | llamada de subrutina individual |

| urdimbre = 32 hilos | Instrucciones SIMD | |||

| Caché L0 de la GPU, registro | hilo (también conocido como "SP", "procesador de transmisión", "núcleo cuda", pero estos nombres ahora están en desuso) | Análogo a las operaciones escalares individuales dentro de una operación vectorial. |

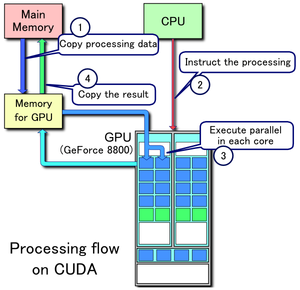

Habilidades de programación

- Copiar datos de la memoria principal a la memoria de la GPU

- La CPU inicia el núcleo de cómputo de la GPU

- Los núcleos CUDA de la GPU ejecutan el kernel en paralelo

- Copiar los datos resultantes de la memoria de la GPU a la memoria principal

La plataforma CUDA es accesible para los desarrolladores de software a través de bibliotecas aceleradas por CUDA, directivas de compilación como OpenACC y extensiones a lenguajes de programación estándar de la industria, incluidos C , C++ , Fortran y Python . Los programadores de C/C++ pueden usar 'CUDA C/C++', compilado en PTX con nvcc , el compilador C/C++ basado en LLVM de Nvidia, o mediante el propio clang. [10] Los programadores de Fortran pueden usar 'CUDA Fortran', compilado con el compilador PGI CUDA Fortran de The Portland Group . [ necesita actualización ] Los programadores de Python pueden usar la biblioteca cuNumeric para acelerar aplicaciones en las GPU de Nvidia.

Además de bibliotecas, directivas de compilador, CUDA C/C++ y CUDA Fortran, la plataforma CUDA admite otras interfaces computacionales, incluyendo OpenCL de Khronos Group , [11] DirectCompute de Microsoft , OpenGL Compute Shader y C++ AMP . [12] También hay disponibles envoltorios de terceros para Python , Perl , Fortran, Java , Ruby , Lua , Common Lisp , Haskell , R , MATLAB , IDL , Julia y soporte nativo en Mathematica .

En la industria de los videojuegos , las GPU se utilizan para la representación de gráficos y para los cálculos de física del juego (efectos físicos como escombros, humo, fuego, fluidos); algunos ejemplos son PhysX y Bullet . CUDA también se ha utilizado para acelerar aplicaciones no gráficas en biología computacional , criptografía y otros campos en un orden de magnitud o más. [13] [14] [15] [16] [17]

CUDA proporciona una API de bajo nivel (CUDA Driver API, no de fuente única) y una API de nivel superior (CUDA Runtime API, de fuente única). El SDK inicial de CUDA se hizo público el 15 de febrero de 2007, para Microsoft Windows y Linux . Posteriormente se agregó compatibilidad con Mac OS X en la versión 2.0, [18] que reemplaza a la versión beta lanzada el 14 de febrero de 2008. [19] CUDA funciona con todas las GPU de Nvidia desde la serie G8x en adelante, incluidas GeForce , Quadro y la línea Tesla . CUDA es compatible con la mayoría de los sistemas operativos estándar.

CUDA 8.0 viene con las siguientes bibliotecas (para compilación y tiempo de ejecución, en orden alfabético):

- cuBLAS – Biblioteca de subrutinas de álgebra lineal básica de CUDA

- CUDART – Biblioteca de ejecución CUDA

- cuFFT – Biblioteca de transformada rápida de Fourier CUDA

- cuRAND – Biblioteca de generación de números aleatorios CUDA

- cuSOLVER: colección de solucionadores directos densos y dispersos basada en CUDA

- cuSPARSE - Biblioteca CUDA Sparse Matrix

- NPP: biblioteca de primitivas de rendimiento de NVIDIA

- nvGRAPH: biblioteca de análisis de gráficos de NVIDIA

- NVML – Biblioteca de administración de NVIDIA

- NVRTC: biblioteca de compilación en tiempo de ejecución de NVIDIA para CUDA C++

CUDA 8.0 viene con estos otros componentes de software:

- nView: software de gestión de escritorio NVIDIA nView

- NVWMI: kit de herramientas de gestión empresarial de NVIDIA

- GameWorks PhysX : es un motor de física de juegos multiplataforma

CUDA 9.0–9.2 viene con estos otros componentes:

- CUTLASS 1.0 – algoritmos de álgebra lineal personalizados,

- NVIDIA Video Decoder quedó obsoleto en CUDA 9.2; ahora está disponible en NVIDIA Video Codec SDK

CUDA 10 viene con estos otros componentes:

- nvJPEG: procesamiento de JPEG híbrido (CPU y GPU)

CUDA 11.0–11.8 viene con estos otros componentes: [20] [21] [22] [23]

- CUB es una de las nuevas bibliotecas de C++ con más soporte

- Compatibilidad con GPU de múltiples instancias MIG

- nvJPEG2000 – Codificador y decodificador JPEG 2000

Ventajas

CUDA tiene varias ventajas sobre el cálculo tradicional de propósito general en GPU (GPGPU) utilizando API de gráficos:

- Lecturas dispersas: el código puede leer desde direcciones arbitrarias en la memoria.

- Memoria virtual unificada (CUDA 4.0 y superior)

- Memoria unificada (CUDA 6.0 y superior)

- Memoria compartida : CUDA expone una región de memoria compartida rápida que puede compartirse entre subprocesos. Esta puede usarse como caché administrada por el usuario, lo que permite un mayor ancho de banda que el que se puede lograr con búsquedas de texturas. [24]

- Descargas y lecturas más rápidas hacia y desde la GPU

- Soporte completo para operaciones de números enteros y bit a bit, incluidas búsquedas de texturas de números enteros

Limitaciones

- Ya sea para el ordenador anfitrión o para el dispositivo GPU, todo el código fuente de CUDA se procesa ahora según las reglas de sintaxis de C++. [25] Este no siempre fue el caso. Las versiones anteriores de CUDA se basaban en las reglas de sintaxis de C. [26] Al igual que con el caso más general de compilar código C con un compilador de C++, es posible que el antiguo código fuente de CUDA de estilo C no se compile o no se comporte como se pretendía originalmente.

- La interoperabilidad con lenguajes de renderizado como OpenGL es unidireccional: OpenGL tiene acceso a la memoria CUDA registrada, pero CUDA no tiene acceso a la memoria OpenGL.

- La copia entre la memoria del host y del dispositivo puede provocar una pérdida de rendimiento debido al ancho de banda del bus del sistema y la latencia (esto se puede aliviar en parte con transferencias de memoria asincrónicas, manejadas por el motor DMA de la GPU).

- Los subprocesos deben ejecutarse en grupos de al menos 32 para obtener el mejor rendimiento, con un número total de subprocesos de miles. Las bifurcaciones en el código del programa no afectan significativamente el rendimiento, siempre que cada uno de los 32 subprocesos tome la misma ruta de ejecución; el modelo de ejecución SIMD se convierte en una limitación significativa para cualquier tarea inherentemente divergente (por ejemplo, atravesar una estructura de datos de partición espacial durante el trazado de rayos ).

- No hay ninguna funcionalidad de emulación o respaldo disponible para las revisiones modernas.

- A veces, el código C++ válido puede quedar marcado y evitar la compilación debido a la forma en que el compilador aborda la optimización para las limitaciones del dispositivo GPU de destino. [ cita requerida ]

- La información de tipo de tiempo de ejecución de C++ (RTTI) y el manejo de excepciones al estilo C++ solo se admiten en el código del host, no en el código del dispositivo.

- En la matemática de precisión simple de los dispositivos de capacidad de cómputo CUDA 1.x de primera generación, los números desnormalizados no son compatibles y, en su lugar, se ponen a cero, y la precisión de las operaciones de división y raíz cuadrada son ligeramente inferiores a las matemáticas de precisión simple compatibles con IEEE 754. Los dispositivos que admiten capacidad de cómputo 2.0 y superiores admiten números desnormalizados, y las operaciones de división y raíz cuadrada son compatibles con IEEE 754 de forma predeterminada. Sin embargo, los usuarios pueden obtener las matemáticas de grado de juego más rápidas anteriores de los dispositivos con capacidad de cómputo 1.x si lo desean, configurando indicadores del compilador para deshabilitar divisiones precisas y raíces cuadradas precisas, y habilitar el vaciado de números desnormalizados a cero. [27]

- A diferencia de OpenCL , las GPU compatibles con CUDA solo están disponibles en Nvidia, ya que es una tecnología propietaria. [28] [1] Los intentos de implementar CUDA en otras GPU incluyen:

- Proyecto Coriander: convierte el código fuente de CUDA C++11 a OpenCL 1.2 C. Una bifurcación de CUDA-on-CL destinada a ejecutar TensorFlow . [29] [30] [31]

- CU2CL: Convierte CUDA 3.2 C++ a OpenCL C. [32]

- GPUOpen HIP: una fina capa de abstracción sobre CUDA y ROCm pensada para GPU AMD y Nvidia. Tiene una herramienta de conversión para importar código fuente CUDA C++. Admite CUDA 4.0 más C++11 y float16.

- ZLUDA es un reemplazo directo de CUDA en las GPU de AMD y, anteriormente, en las GPU de Intel con un rendimiento casi nativo. [33] El desarrollador, Andrzej Janik, fue contratado por separado tanto por Intel como por AMD para desarrollar el software en 2021 y 2022, respectivamente. Sin embargo, ninguna de las empresas decidió lanzarlo oficialmente debido a la falta de un caso de uso comercial. El contrato de AMD incluía una cláusula que permitía a Janik publicar su código para AMD de forma independiente, lo que le permitía lanzar la nueva versión que solo es compatible con las GPU de AMD. [34]

- chipStar puede compilar y ejecutar programas CUDA/HIP en plataformas avanzadas OpenCL 3.0 o Level Zero. [35]

Ejemplo

Este código de ejemplo en C++ carga una textura de una imagen en una matriz en la GPU:

textura < float , 2 , cudaReadModeElementType > tex ; void foo () { cudaArray * cu_array ; // Asignar matriz cudaChannelFormatDesc descripción = cudaCreateChannelDesc < float > (); cudaMallocArray ( & cu_array , & descripción , ancho , alto ); // Copiar datos de imagen a la matriz cudaMemcpyToArray ( cu_array , image , width * height * sizeof ( float ), cudaMemcpyHostToDevice ); // Establecer parámetros de textura (predeterminado) tex . addressMode [ 0 ] = cudaAddressModeClamp ; tex . addressMode [ 1 ] = cudaAddressModeClamp ; tex . filterMode = cudaFilterModePoint ; tex . normalized = false ; // no normalizar las coordenadas // Vincula la matriz a la textura cudaBindTextureToArray ( tex , cu_array ); // Ejecutar kernel dim3 blockDim ( 16 , 16 , 1 ); dim3 gridDim (( ancho + blockDim . x - 1 ) / blockDim . x , ( alto + blockDim . y - 1 ) / blockDim . y , 1 ); kernel <<< gridDim , blockDim , 0 >>> ( d_data , alto , ancho ); // Desvincular la matriz de la textura cudaUnbindTexture ( tex ); } //fin foo() __global__ void kernel ( float * odata , int altura , int ancho ) { entero sin signo x = blockIdx.x * blockDim.x + threadIdx.x ; entero sin signo y = blockIdx.y * blockDim.y + threadIdx.y ; if ( x < ancho && y < alto ) { float c = tex2D ( tex , x , y ) ; odata [ y * ancho + x ] = c ; } } A continuación se muestra un ejemplo en Python que calcula el producto de dos matrices en la GPU. Los enlaces no oficiales del lenguaje Python se pueden obtener de PyCUDA . [36]

importar pycuda.compiler como comp importar pycuda.driver como drv importar numpy importar pycuda.autoinitmod = comp . MóduloOrigen ( """ __global__ void multiplicarlos(float *dest, float *a, float *b) { const int i = threadIdx.x; dest[i] = a[i] * b[i]; } """ ) multiplicarlos = mod . get_function ( "multiplicarlos" )a = numpy . random . randn ( 400 ) . astype ( numpy . float32 ) b = numpy . random . randn ( 400 ) . astype ( numpy . float32 )dest = numpy . ceros_similares ( a ) multiplicarlos ( drv . salida ( dest ), drv . entrada ( a ), drv . entrada ( b ), bloque = ( 400 , 1 , 1 ))imprimir ( dest - a * b )Se pueden encontrar enlaces de Python adicionales para simplificar las operaciones de multiplicación de matrices en el programa pycublas . [37]

importar numpy desde pycublas importar CUBLASMatrixA = MatrizCUBLAS ( numpy.mat ( [ [ 1,2,3 ] , [ 4,5,6 ] ] , numpy.float32 ) ) B = MatrizCUBLAS ( numpy.mat ( [ [ 2,3 ] , [ 4,5 ] , [ 6,7 ] ] , numpy.float32 ) ) C = A * B print ( C.np_mat ( ) ) mientras que CuPy reemplaza directamente a NumPy: [38]

Importar cupya = cupy . aleatorio . randn ( 400 ) b = cupy . aleatorio . randn ( 400 )destino = cupy . ceros_como ( a )imprimir ( dest - a * b )GPU compatibles

Versiones de capacidad de cómputo CUDA compatibles con la versión del SDK de CUDA y la microarquitectura (por nombre de código):

Versiones del SDK de CUDA | Tesla | Fermi | Kepler (temprano) | Kepler (finales) | Maxwell | Pascal | Vuelta | Turing | Amperio | Ada Lovelace | Tolva | Pozo negro |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1.0 [39] | 1.0 – 1.1 | |||||||||||

| 1.1 | 1.0 – 1.1+x | |||||||||||

| 2.0 | 1.0 – 1.1+x | |||||||||||

| 2.1 – 2.3.1 [40] [41] [42] [43] | 1.0 – 1.3 | |||||||||||

| 3.0 – 3.1 [44] [45] | 1.0 | 2.0 | ||||||||||

| 3.2 [46] | 1.0 | 2.1 | ||||||||||

| 4.0 – 4.2 | 1.0 | 2.1 | ||||||||||

| 5.0 – 5.5 | 1.0 | 3.5 | ||||||||||

| 6.0 | 1.0 | 3.2 | 3.5 | |||||||||

| 6.5 | 1.1 | 3.7 | 5.x | |||||||||

| 7.0 – 7.5 | 2.0 | 5.x | ||||||||||

| 8.0 | 2.0 | 6.x | ||||||||||

| 9.0 – 9.2 | 3.0 | 7.0 – 7.2 | ||||||||||

| 10.0 – 10.2 | 3.0 | 7.5 | ||||||||||

| 11.0 [47] | 3.5 | 8.0 | ||||||||||

| 11.1 – 11.4 [48] | 3.5 | 8.6 | ||||||||||

| 11.5 – 11.7.1 [49] | 3.5 | 8.7 | ||||||||||

| 11.8 [50] | 3.5 | 8.9 | 9.0 | |||||||||

| 12.0 – 12.5 | 5.0 | 9.0 |

Nota: CUDA SDK 10.2 es la última versión oficial para macOS, ya que el soporte no estará disponible para macOS en versiones más nuevas.

Capacidad de cómputo de CUDA por versión con semiconductores de GPU asociados y modelos de tarjetas GPU (separados por sus diversas áreas de aplicación):

Capacidad de cómputo (versión) | Microarquitectura | GPU | GeForce | Cuadro , NVS | Tesla/Centro de datos | Tegra , Jetson , UNIDAD |

|---|---|---|---|---|---|---|

| 1.0 | Tesla | G80 | GeForce 8800 Ultra, GeForce 8800 GTX, GeForce 8800 GTS (G80) | Quadro FX 5600, Quadro FX 4600, Quadro Plex 2100 S4 | Tesla C870, Tesla D870, Tesla S870 | |

| 1.1 | G92, G94, G96, G98, G84, G86 | GeForce GTS 250, GeForce 9800 GX2, GeForce 9800 GTX, GeForce 9800 GT, GeForce 8800 GTS (G92), GeForce 8800 GT, GeForce 9600 GT, GeForce 9500 GT, GeForce 9400 GT, GeForce 8600 GTS, GeForce 8600 GT, GeForce 8500 GT, GeForce G110M, GeForce 9300M GS, GeForce 9200M GS, GeForce 9100M G, GeForce 8400M GT, GeForce G105M | Quadro FX 4700 X2, Quadro FX 3700, Quadro FX 1800, Quadro FX 1700, Quadro FX 580, Quadro FX 570, Quadro FX 470, Quadro FX 380, Quadro FX 370, Quadro FX 370 de perfil bajo, Quadro NVS 450, Quadro NVS 420, Quadro NVS 290, Quadro NVS 295, Quadro Plex 2100 D4, Quadro FX 3800M, Quadro FX 3700M, Quadro FX 3600M, Quadro FX 2800M, Quadro FX 2700M, Quadro FX 1700M, Quadro FX 1600M, Quadro FX 770M, Quadro FX 570M, Quadro FX 370M, Quadro FX 360M, Cámaras de video Quadro NVS 320M, Cámaras de video Quadro NVS 160M, Cámaras de video Quadro NVS 150M, Cámaras de video Quadro NVS 140M, Cámaras de video Quadro NVS 135M, Cámaras de video Quadro NVS 130M, Cámaras de video Quadro NVS 450, Cámaras de video Quadro NVS 420, [51] Cámaras de video Quadro NVS 295 | |||

| 1.2 | GT218, GT216, GT215 | GeForce GT 340*, GeForce GT 330*, GeForce GT 320*, GeForce 315*, GeForce 310*, GeForce GT 240, GeForce GT 220, GeForce 210, GeForce GTS 360M, GeForce GTS 350M, GeForce GT 335M, GeForce GT 330M, GeForce GT 325M, GeForce GT 240M, GeForce G210M, GeForce 310M, GeForce 305M | Quadro FX 380 de perfil bajo, Quadro FX 1800M, Quadro FX 880M, Quadro FX 380M, Nvidia NVS 300, NVS 5100M, NVS 3100M, NVS 2100M, ION | |||

| 1.3 | GT200, GT200b | GeForce GTX 295, GTX 285, GTX 280, GeForce GTX 275, GeForce GTX 260 | Quadro FX 5800, Quadro FX 4800, Quadro FX 4800 para Mac, Quadro FX 3800, Quadro CX, Quadro Plex 2200 D2 | Tesla C1060, Tesla S1070, Tesla M1060 | ||

| 2.0 | Fermi | GF100, GF110 | GeForce GTX 590, GeForce GTX 580, GeForce GTX 570, GeForce GTX 480, GeForce GTX 470, GeForce GTX 465, GeForce GTX 480M | Quadro 6000, Quadro 5000, Quadro 4000, Quadro 4000 para Mac, Quadro Plex 7000, Quadro 5010M, Quadro 5000M | Tesla C2075, Tesla C2050/C2070, Tesla M2050/M2070/M2075/M2090 | |

| 2.1 | GF104, GF106, GF108, GF114, GF116, GF117, GF119 | GeForce GTX 560 Ti, GeForce GTX 550 Ti, GeForce GTX 460, GeForce GTS 450, GeForce GTS 450*, GeForce GT 640 (GDDR3), GeForce GT 630, GeForce GT 620, GeForce GT 610, GeForce GT 520, GeForce GT 440, GeForce GT 440*, GeForce GT 430, GeForce GT 430*, GeForce GT 420*, GeForce GTX 675M, GeForce GTX 670M, GeForce GT 635M, GeForce GT 630M, GeForce GT 625M, GeForce GT 720M, GeForce GT 620M, GeForce 710M, GeForce 610M, GeForce 820M, GeForce GTX 580M, GeForce GTX 570M, GeForce GTX 560M, GeForce GT 555M, GeForce GT 550M, GeForce GT 540M, GeForce GT 525M, GeForce GT 520MX, GeForce GT 520M, GeForce GTX 485M, GeForce GTX 470M, GeForce GTX 460M, GeForce GT 445M, GeForce GT 435M, GeForce GT 420M, GeForce GT 415M, GeForce 710M, GeForce 410M | Cámaras Quadro 2000, Quadro 2000D, Quadro 600, Quadro 4000M, Quadro 3000M, Quadro 2000M, Quadro 1000M, NVS 310, NVS 315, NVS 5400M, NVS 5200M, NVS 4200M | |||

| 3.0 | Kepler | GK104, GK106, GK107 | GeForce GTX 770, GeForce GTX 760, GeForce GT 740, GeForce GTX 690, GeForce GTX 680, GeForce GTX 670, GeForce GTX 660 Ti, GeForce GTX 660, GeForce GTX 650 Ti BOOST, GeForce GTX 650 Ti, GeForce GTX 650, GeForce GTX 880M, GeForce GTX 870M, GeForce GTX 780M, GeForce GTX 770M, GeForce GTX 765M, GeForce GTX 760M, GeForce GTX 680MX, GeForce GTX 680M, GeForce GTX 675MX, GeForce GTX 670MX, GeForce GTX 660M, GeForce GT 750M, GeForce GT 650M, GeForce GT 745M, GeForce GT 645M, GeForce GT 740M, GeForce GT 730M, GeForce GT 640M, GeForce GT 640M LE, GeForce GT 735M, GeForce GT 730M | Cámaras digitales: Quadro K5000, Quadro K4200, Quadro K4000, Quadro K2000, Quadro K2000D, Quadro K600, Quadro K420, Quadro K500M, Quadro K510M, Quadro K610M, Quadro K1000M, Quadro K2000M, Quadro K1100M, Quadro K2100M, Quadro K3000M, Quadro K3100M, Quadro K4000M, Quadro K5000M, Quadro K4100M, Quadro K5100M, NVS 510, Quadro 410 | Tesla K10, RED K340, RED K520, RED K2 | |

| 3.2 | GK20A | Tegra K1, Jetson TK1 | ||||

| 3.5 | GK110, GK208 | GeForce GTX Titan Z, GeForce GTX Titan Black, GeForce GTX Titan, GeForce GTX 780 Ti, GeForce GTX 780, GeForce GT 640 (GDDR5), GeForce GT 630 v2, GeForce GT 730, GeForce GT 720, GeForce GT 710, GeForce GT 740M (64 bits, DDR3), GeForce GT 920M | Cámaras Quadro K6000 y Quadro K5200 | Tesla K40, Tesla K20x, Tesla K20 | ||

| 3.7 | GK210 | Tesla K80 | ||||

| 5.0 | Maxwell | GM107, GM108 | GeForce GTX 750 Ti, GeForce GTX 750, GeForce GTX 960M, GeForce GTX 950M, GeForce 940M, GeForce 930M, GeForce GTX 860M, GeForce GTX 850M, GeForce 845M, GeForce 840M, GeForce 830M | Cámaras Quadro K1200, Quadro K2200, Quadro K620, Quadro M2000M, Quadro M1000M, Quadro M600M, Quadro K620M y NVS 810 | Tesla M10 | |

| 5.2 | GM200, GM204, GM206 | GeForce GTX Titan X, GeForce GTX 980 Ti, GeForce GTX 980, GeForce GTX 970, GeForce GTX 960, GeForce GTX 950, GeForce GTX 750 SE, GeForce GTX 980M, GeForce GTX 970M, GeForce GTX 965M | Quadro M6000 de 24 GB, Quadro M6000, Quadro M5000, Quadro M4000, Quadro M2000, Quadro M5500, Quadro M5000M, Quadro M4000M, Quadro M3000M | Tesla M4, Tesla M40, Tesla M6, Tesla M60 | ||

| 5.3 | GM20B | Tegra X1, Jetson TX1, Jetson Nano, DRIVE CX, DRIVE PX | ||||

| 6.0 | Pascal | GP100 | Cámara Quadro GP100 | Tesla P100 | ||

| 6.1 | GP102, GP104, GP106, GP107, GP108 | Nvidia TITAN Xp, Titan X, GeForce GTX 1080 Ti, GTX 1080, GTX 1070 Ti, GTX 1070, GTX 1060, GTX 1050 Ti, GTX 1050, GT 1030, GT 1010, MX350, MX330, MX250, MX230, MX150, MX130, MX110 | Quadro P6000, Quadro P5000, Quadro P4000, Quadro P2200, Quadro P2000, Quadro P1000, Quadro P400, Quadro P500, Quadro P520, Quadro P600, Quadro P5000 (móvil), Quadro P4000 (móvil), Quadro P3000 (móvil) | Tesla P40, Tesla P6, Tesla P4 | ||

| 6.2 | GP10B [52] | Tegra X2, Jetson TX2, UNIDAD PX 2 | ||||

| 7.0 | Vuelta | GV100 | NVIDIA TITAN V | Cámara Quadro GV100 | Tesla V100, Tesla V100S | |

| 7.2 | GV10B [53] GV11B [54] [55] | Tegra Xavier, Jetson Xavier NX, Jetson AGX Xavier, DRIVE AGX Xavier, DRIVE AGX Pegasus, Clara AGX | ||||

| 7.5 | Turing | TU102, TU104, TU106, TU116, TU117 | NVIDIA TITAN RTX, GeForce RTX 2080 Ti, RTX 2080 Super, RTX 2080, RTX 2070 Super, RTX 2070, RTX 2060 Super, RTX 2060 12 GB, RTX 2060, GeForce GTX 1660 Ti, GTX 1660 Super, GTX 1660, GTX 1650 Super, GTX 1650, MX550, MX450 | Quadro RTX 8000, Quadro RTX 6000, Quadro RTX 5000, Quadro RTX 4000, T1000, T600, T400 T1200 (móvil), T600 (móvil), T500 (móvil), Quadro T2000 (móvil), Quadro T1000 (móvil) | Tesla T4 | |

| 8.0 | Amperio | GA100 | A100 de 80 GB, A100 de 40 GB, A30 | |||

| 8.6 | GA102, GA103, GA104, GA106, GA107 | GeForce RTX 3090 Ti, RTX 3090, RTX 3080 Ti, RTX 3080 12 GB, RTX 3080, RTX 3070 Ti, RTX 3070, RTX 3060 Ti, RTX 3060, RTX 3050, RTX 3050 Ti (móvil), RTX 3050 (móvil), RTX 2050 (móvil), MX570 | RTX A6000, RTX A5500, RTX A5000, RTX A4500, RTX A4000, RTX A2000 RTX A5000 (móvil), RTX A4000 (móvil), RTX A3000 (móvil), RTX A2000 (móvil) | A40, A16, A10, A2 | ||

| 8.7 | GA10B | Jetson Orin Nano, Jetson Orin NX, Jetson AGX Orin, DRIVE AGX Orin, DRIVE AGX Pegasus OA, Clara Holoscan | ||||

| 8.9 | Ada Lovelace [56] | 102 d. C., 103 d. C., 104 d. C., 106 d. C., 107 d. C. | GeForce RTX 4090, RTX 4080 Super, RTX 4080, RTX 4070 Ti Super, RTX 4070 Ti, RTX 4070 Super, RTX 4070, RTX 4060 Ti, RTX 4060 | RTX 6000 Ada, RTX 5880 Ada, RTX 5000 Ada, RTX 4500 Ada, RTX 4000 Ada, RTX 4000 SFF | L40S, L40, L20, L4, L2 | |

| 9.0 | Tolva | GH100 | H200, H100 | |||

| 10.0 | Pozo negro | GB100 | B200, B100 | |||

| 10.x | GB202, GB203, GB205, GB206, GB207 | GeForce RTX 5090, RTX 5080 | B40 | |||

Capacidad de cómputo (versión) | Microarquitectura | GPU | GeForce | Cuadro , NVS | Tesla/Centro de datos | Tegra , Jetson , UNIDAD |

'*' – Productos exclusivos de OEM

Características y especificaciones de la versión

This section needs to be updated. The reason given is: Missing CUDA compute capability 10.x (Blackwell). (March 2024) |

| Compatibilidad con funciones (las funciones no incluidas en la lista son compatibles con todas las capacidades informáticas) | Capacidad de cómputo (versión) | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1.0, 1.1 | 1.2, 1.3 | 2.x | 3.0 | 3.2 | 3.5, 3.7, 5.x, 6.x, 7.0, 7.2 | 7.5 | 8.x | 9.0 | ||||||

| Funciones de votación de deformación (__all(), __any()) | No | Sí | ||||||||||||

| Funciones de votación de deformación (__ballot()) | No | Sí | ||||||||||||

| Funciones de protección de memoria (__threadfence_system()) | ||||||||||||||

| Funciones de sincronización (__syncthreads_count(), __syncthreads_and(), __syncthreads_or()) | ||||||||||||||

| Funciones de superficie | ||||||||||||||

| Cuadrícula 3D de bloques de hilos | ||||||||||||||

| Funciones de barajado de deformación | No | Sí | ||||||||||||

| Programación de memoria unificada | ||||||||||||||

| Cambio de embudo | No | Sí | ||||||||||||

| Paralelismo dinámico | No | Sí | ||||||||||||

| Ruta de datos uniforme [57] | No | Sí | ||||||||||||

| Copia asincrónica acelerada por hardware | No | Sí | ||||||||||||

| Barrera de llegada/espera dividida acelerada por hardware | ||||||||||||||

| Soporte de nivel Warp para operaciones de reducción | ||||||||||||||

| Gestión de la residencia de caché L2 | ||||||||||||||

| Instrucciones DPX para programación dinámica acelerada | No | Sí | ||||||||||||

| Memoria compartida distribuida | ||||||||||||||

| Clúster de bloques de subprocesos | ||||||||||||||

| Unidad aceleradora de memoria tensorial (TMA) | ||||||||||||||

| Compatibilidad con funciones (las funciones no incluidas en la lista son compatibles con todas las capacidades informáticas) | 1.0,1.1 | 1.2,1.3 | 2.x | 3.0 | 3.2 | 3.5, 3.7, 5.x, 6.x, 7.0, 7.2 | 7.5 | 8.x | 9.0 | |||||

| Capacidad de cómputo (versión) | ||||||||||||||

[58]

Tipos de datos

| Tipo de datos | Operación | Con soporte desde | Operación atómica | Compatible desde entonces para memoria global | Compatible desde entonces para memoria compartida |

|---|---|---|---|---|---|

| Entero de 8 bits con signo o sin signo | carga, almacenamiento, conversión | 1.0 | — | — | |

| Entero de 16 bits con signo o sin signo | operaciones generales | 1.0 | CAS atómico() | 3.5 | |

| Entero de 32 bits con signo o sin signo | operaciones generales | 1.0 | funciones atómicas | 1.1 | 1.2 |

| Entero de 64 bits con signo o sin signo | operaciones generales | 1.0 | funciones atómicas | 1.2 | 2.0 |

| Cualquier tipo de 128 bits que se pueda copiar de forma trivial | operaciones generales | No | intercambio atómico, CAS atómico | 9.0 | |

FP16 de punto flotante de 16 bits | suma, resta, multiplicación, comparación, funciones de mezcla de deformación, conversión | 5.3 | adición atómica half2 | 6.0 | |

| adición atómica | 7.0 | ||||

BF16 de punto flotante de 16 bits | suma, resta, multiplicación, comparación, funciones de mezcla de deformación, conversión | 8.0 | adición atómica | 8.0 | |

| Punto flotante de 32 bits | operaciones generales | 1.0 | Excambio atómico () | 1.1 | 1.2 |

| adición atómica | 2.0 | ||||

| Coma flotante de 32 bits float2 y float4 | operaciones generales | No | adición atómica | 9.0 | |

| Punto flotante de 64 bits | operaciones generales | 1.3 | adición atómica | 6.0 | |

Nota: Cualquier línea faltante o entrada vacía refleja cierta falta de información sobre ese elemento exacto. [59]

Núcleos tensoriales

| FMA por ciclo por núcleo tensor [60] | Con soporte desde | 7.0 | 7.2 | 7.5 Estación de trabajo | 7.5 Escritorio | 8.0 | 8.6 Estación de trabajo | 8.7 | 8.9 Estación de trabajo | 8.6 Escritorio | 8.9 Escritorio | 9.0 | 10.0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Tipo de datos | Para matrices densas | Para matrices dispersas | 1.ª generación (8x/SM) | 1.ª generación? (8x/SM) | 2.ª generación (8x/SM) | 3.ª generación (4x/SM) | Cuarta generación (4x/SM) | 3.ª generación (4x/SM) | Cuarta generación (4x/SM) | 5.ª generación (4x/SM) | ||||

| Valores de 1 bit (AND) | 8.0 como experimental | No | No | 4096 | 2048 | 4096 | Velocidad por determinar | |||||||

| Valores de 1 bit (XOR) | 7,5–8,9 como experimental | No | 1024 | ¿Obsoleto o eliminado? | ||||||||||

| Enteros de 4 bits | 8.0–8.9 como experimental | 256 | 1024 | 512 | 1024 | |||||||||

| FP4 de punto flotante de 4 bits (E2M1?) | 10.0 | No | 4096 | |||||||||||

| FP6 de punto flotante de 6 bits (¿E3M2 y E2M3?) | 10.0 | No | 2048 | |||||||||||

| Enteros de 8 bits | 7.2 | 8.0 | No | 128 | 128 | 512 | 256 | 512 | 1024 | 2048 | ||||

| FP8 de punto flotante de 8 bits (E4M3 y E5M2) con acumulación FP16 | 8.9 | No | 512 | No | ||||||||||

| FP8 de punto flotante de 8 bits (E4M3 y E5M2) con acumulación FP32 | ||||||||||||||

| FP16 de punto flotante de 16 bits con acumulación de FP16 | 7.0 | 8.0 | 64 | 64 | 64 | 256 | 128 | 256 | 512 | 1024 | ||||

| FP16 de punto flotante de 16 bits con acumulación FP32 | 32 | 64 | 128 | |||||||||||

| BF16 de punto flotante de 16 bits con acumulación FP32 | 7.5 [61] | 8.0 | No | |||||||||||

| Punto flotante TF32 de 32 bits (se utilizan 19 bits) | velocidad por determinar (32?) | 128 | 32 | 64 | 256 | 512 | ||||||||

| Punto flotante de 64 bits | 8.0 | No | No | 16 | Velocidad por determinar | 32 | 16 | |||||||

Nota: Cualquier línea faltante o entrada vacía refleja cierta falta de información sobre ese elemento exacto. [62] [63] [64] [65] [66] [67]

| Composición del núcleo tensorial | 7.0 | 7.2, 7.5 | 8.0, 8.6 | 8.7 | 8.9 | 9.0 |

|---|---|---|---|---|---|---|

| Ancho de unidad del producto escalar en unidades FP16 (en bytes) [68] [69] [70] [71] | 4 (8) | 8 (16) | 4 (8) | 16 (32) | ||

| Unidades del producto escalar por núcleo tensorial | 16 | 32 | ||||

| Núcleos tensores por partición SM | 2 | 1 | ||||

| Rendimiento total (bytes/ciclo) [72] por partición SM [73] | 256 | 512 | 256 | 1024 | ||

| Núcleos tensoriales FP: ciclos mínimos para el cálculo de matrices de toda la deformación | 8 | 4 | 8 | |||

| Núcleos tensoriales FP: forma de matriz mínima para rendimiento completo (bytes) [74] | 2048 | |||||

| Núcleos tensoriales INT: ciclos mínimos para el cálculo de matrices de toda la deformación | No | 4 | ||||

| Núcleos tensoriales INT: forma de matriz mínima para rendimiento completo (bytes) | No | 1024 | 2048 | 1024 | ||

[75] [76] [77] [78]

| Composición del núcleo tensorial FP64 | 8.0 | 8.6 | 8.7 | 8.9 | 9.0 |

|---|---|---|---|---|---|

| Ancho de unidad del producto escalar en unidades FP64 (en bytes) | 4 (32) | Por determinar | 4 (32) | ||

| Unidades del producto escalar por núcleo tensorial | 4 | Por determinar | 8 | ||

| Núcleos tensores por partición SM | 1 | ||||

| Rendimiento total (bytes/ciclo) [79] por partición SM [80] | 128 | Por determinar | 256 | ||

| Ciclos mínimos para el cálculo de la matriz de curvatura completa | 16 | Por determinar | |||

| Forma mínima de la matriz para rendimiento completo (bytes) [81] | 2048 | ||||

Especificaciones técnicas

| Especificaciones técnicas | Capacidad de cómputo (versión) | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1.0 | 1.1 | 1.2 | 1.3 | 2.x | 3.0 | 3.2 | 3.5 | 3.7 | 5.0 | 5.2 | 5.3 | 6.0 | 6.1 | 6.2 | 7.0 | 7.2 | 7.5 | 8.0 | 8.6 | 8.7 | 8.9 | 9.0 | |

| Número máximo de cuadrículas residentes por dispositivo (ejecución de kernel simultánea, puede ser menor para dispositivos específicos) | 1 | 16 | 4 | 32 | 16 | 128 | 32 | 16 | 128 | 16 | 128 | ||||||||||||

| Máxima dimensionalidad de la cuadrícula de bloques de hilos | 2 | 3 | |||||||||||||||||||||

| Dimensión x máxima de una cuadrícula de bloques de hilos | 65535 | 2 31 − 1 | |||||||||||||||||||||

| Dimensión máxima y o z de una cuadrícula de bloques de hilos | 65535 | ||||||||||||||||||||||

| Máxima dimensionalidad del bloque de rosca | 3 | ||||||||||||||||||||||

| Dimensión máxima x o y de un bloque | 512 | 1024 | |||||||||||||||||||||

| Dimensión z máxima de un bloque | 64 | ||||||||||||||||||||||

| Número máximo de subprocesos por bloque | 512 | 1024 | |||||||||||||||||||||

| Tamaño de la urdimbre | 32 | ||||||||||||||||||||||

| Número máximo de bloques residentes por multiprocesador | 8 | 16 | 32 | 16 | 32 | 16 | 24 | 32 | |||||||||||||||

| Número máximo de warps residentes por multiprocesador | 24 | 32 | 48 | 64 | 32 | 64 | 48 | 64 | |||||||||||||||

| Número máximo de subprocesos residentes por multiprocesador | 768 | 1024 | 1536 | 2048 | 1024 | 2048 | 1536 | 2048 | |||||||||||||||

| Número de registros regulares de 32 bits por multiprocesador | 8 kilógramos | 16 mil | 32 mil | 64 kilógramos | 128 kilógramos | 64 kilógramos | |||||||||||||||||

| Número de registros uniformes de 32 bits por multiprocesador | No | 2 K [82] [83] | |||||||||||||||||||||

| Número máximo de registros de 32 bits por bloque de subproceso | 8 kilógramos | 16 mil | 32 mil | 64 kilógramos | 32 mil | 64 kilógramos | 32 mil | 64 kilógramos | 32 mil | 64 kilógramos | |||||||||||||

| Número máximo de registros regulares de 32 bits por hilo | 124 | 63 | 255 | ||||||||||||||||||||

| Número máximo de registros uniformes de 32 bits por warp | No | 63 [84] [85] | |||||||||||||||||||||

| Cantidad de memoria compartida por multiprocesador (de la memoria compartida total + caché L1, cuando corresponda) | 16 KiB | 16 / 48 KiB (de 64 KiB) | 16 / 32 / 48 KiB (de 64 KiB) | 80 / 96 / 112 KiB (de 128 KiB) | 64 KiB | 96 KiB | 64 KiB | 96 KiB | 64 KiB | 0 / 8 / 16 / 32 / 64 / 96 KiB (de 128 KiB) | 32 / 64 KiB (de 96 KiB) | 0 / 8 / 16 / 32 / 64 / 100 / 132 / 164 KiB (de 192 KiB) | 0 / 8 / 16 / 32 / 64 / 100 KiB (de 128 KiB) | 0 / 8 / 16 / 32 / 64 / 100 / 132 / 164 KiB (de 192 KiB) | 0 / 8 / 16 / 32 / 64 / 100 KiB (de 128 KiB) | 0 / 8 / 16 / 32 / 64 / 100 / 132 / 164 / 196 / 228 KiB (de 256 KiB) | |||||||

| Cantidad máxima de memoria compartida por bloque de subproceso | 16 KiB | 48 KiB | 96 KiB | 48 KiB | 64 KiB | 163 KiB | 99 KiB | 163 KiB | 99 KiB | 227 KiB | |||||||||||||

| Número de bancos de memoria compartida | 16 | 32 | |||||||||||||||||||||

| Cantidad de memoria local por hilo | 16 KiB | 512 KiB | |||||||||||||||||||||

| Tamaño de memoria constante accesible por CUDA C/C++ (1 banco, PTX puede acceder a 11 bancos, SASS puede acceder a 18 bancos) | 64 KiB | ||||||||||||||||||||||

| Conjunto de trabajo de caché por multiprocesador para memoria constante | 8 KiB | 4 KiB | 8 KiB | ||||||||||||||||||||

| Conjunto de trabajo de caché por multiprocesador para memoria de textura | 16 KiB por TPC | 24 KiB por TPC | 12 KiB | 12 – 48 KiB [86] | 24 KiB | 48 KiB | 32 KiB [87] | 24 KiB | 48 KiB | 24 KiB | 32 – 128 KiB | 32 – 64 KiB | 28 – 192 KiB | 28 – 128 KiB | 28 – 192 KiB | 28 – 128 KiB | 28 – 256 KiB | ||||||

| Ancho máximo para la referencia de textura 1D vinculada a una matriz CUDA | 8192 | 65536 | 131072 | ||||||||||||||||||||

| Ancho máximo para la referencia de textura 1D vinculada a la memoria lineal | 2 27 | 2 28 | 2 27 | 2 28 | 2 27 | 2 28 | |||||||||||||||||

| Ancho máximo y número de capas para una referencia de textura en capas 1D | 8192 × 512 | 16384 × 2048 | 32768 x 2048 | ||||||||||||||||||||

| Ancho y alto máximos para la referencia de textura 2D vinculada a una matriz CUDA | 65536 × 32768 | 65536 × 65535 | 131072 x 65536 | ||||||||||||||||||||

| Ancho y alto máximos para la referencia de textura 2D vinculada a una memoria lineal | 65000 x 65000 | 65536 x 65536 | 131072 x 65000 | ||||||||||||||||||||

| Ancho y alto máximos para la referencia de textura 2D vinculada a una matriz CUDA que admite la recopilación de texturas | — | 16384 x 16384 | 32768 x 32768 | ||||||||||||||||||||

| Ancho, altura y número máximos de capas para una referencia de textura en capas 2D | 8192 × 8192 × 512 | 16384 × 16384 × 2048 | 32768 x 32768 x 2048 | ||||||||||||||||||||

| Ancho, altura y profundidad máximos para una referencia de textura 3D vinculada a una memoria lineal o una matriz CUDA | 2048 3 | 4096 3 | 16384 3 | ||||||||||||||||||||

| Ancho (y alto) máximo para una referencia de textura de mapa cúbico | — | 16384 | 32768 | ||||||||||||||||||||

| Ancho máximo (y alto) y número de capas para una referencia de textura en capas de mapa cúbico | — | 16384 × 2046 | 32768 × 2046 | ||||||||||||||||||||

| Número máximo de texturas que se pueden vincular a un núcleo | 128 | 256 | |||||||||||||||||||||

| Ancho máximo para una referencia de superficie 1D vinculada a una matriz CUDA | No soportado | 65536 | 16384 | 32768 | |||||||||||||||||||

| Ancho máximo y número de capas para una referencia de superficie en capas 1D | 65536 × 2048 | 16384 × 2048 | 32768 × 2048 | ||||||||||||||||||||

| Ancho y alto máximos para una referencia de superficie 2D vinculada a una matriz CUDA | 65536 × 32768 | 16384 × 65536 | 131072 × 65536 | ||||||||||||||||||||

| Ancho, altura y número máximos de capas para una referencia de superficie en capas 2D | 65536 × 32768 × 2048 | 16384 × 16384 × 2048 | 32768 × 32768 × 2048 | ||||||||||||||||||||

| Ancho, altura y profundidad máximos para una referencia de superficie 3D vinculada a una matriz CUDA | 65536 × 32768 × 2048 | 4096 × 4096 × 4096 | 16384 × 16384 × 16384 | ||||||||||||||||||||

| Ancho (y alto) máximo para una referencia de superficie de mapa cúbico vinculada a una matriz CUDA | 32768 | 16384 | 32768 | ||||||||||||||||||||

| Ancho máximo y número de capas para una referencia de superficie en capas de mapa cúbico | 32768 × 2046 | 16384 × 2046 | 32768 × 2046 | ||||||||||||||||||||

| Número máximo de superficies que se pueden vincular a un núcleo | 8 | 16 | 32 | ||||||||||||||||||||

| Número máximo de instrucciones por núcleo | 2 millones | 512 millones | |||||||||||||||||||||

| Número máximo de bloques de subprocesos por grupo de bloques de subprocesos [88] | No | 16 | |||||||||||||||||||||

| Especificaciones técnicas | 1.0 | 1.1 | 1.2 | 1.3 | 2.x | 3.0 | 3.2 | 3.5 | 3.7 | 5.0 | 5.2 | 5.3 | 6.0 | 6.1 | 6.2 | 7.0 | 7.2 | 7.5 | 8.0 | 8.6 | 8.7 | 8.9 | 9.0 |

| Capacidad de cómputo (versión) | |||||||||||||||||||||||

[90]

Arquitectura multiprocesador

| Especificaciones de arquitectura | Capacidad de cómputo (versión) | |||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1.0 | 1.1 | 1.2 | 1.3 | 2.0 | 2.1 | 3.0 | 3.2 | 3.5 | 3.7 | 5.0 | 5.2 | 5.3 | 6.0 | 6.1 | 6.2 | 7.0 | 7.2 | 7.5 | 8.0 | 8.6 | 8.7 | 8.9 | 9.0 | |

| Número de carriles ALU para operaciones aritméticas INT32 | 8 | 32 | 48 | 192 [91] | 128 | 128 | 64 | 128 | 128 | 64 | 64 | 64 | ||||||||||||

| Número de carriles ALU para cualquier operación aritmética INT32 o FP32 | — | — | ||||||||||||||||||||||

| Número de carriles ALU para operaciones aritméticas FP32 | 64 | 64 | 128 | 128 | ||||||||||||||||||||

| Número de carriles de ALU para operaciones aritméticas FP16x2 | No | 1 | 128 [92] | 128 [93] | 64 [94] | |||||||||||||||||||

| Número de carriles ALU para operaciones aritméticas FP64 | No | 1 | 16 por FP32 [95] | 4 por FP32 [96] | 8 | 8 / 64 [97] | 64 | 4 [98] | 32 | 4 | 32 | 2 | 32 | 2 | 2? | 2 | 64 | |||||||

| Número de unidades de carga/almacenamiento | 4 por 2 SM | 8 por 2 SM | 8 por 2 SM / 3 SM [97] | 8 por 3 SM | 16 | 32 | 16 | 32 | 16 | 32 | ||||||||||||||

| Número de unidades de funciones especiales para funciones trascendentales de punto flotante de precisión simple | 2 [99] | 4 | 8 | 32 | 16 | 32 | 16 | |||||||||||||||||

| Número de unidades de mapeo de textura (TMU) | 4 por 2 SM | 8 por 2 SM | 8 por 2/3SM [97] | 8 por 3 SM | 4 | 4 / 8 [97] | 16 | 8 | 16 | 8 | 4 | |||||||||||||

| Número de carriles de ALU para operaciones aritméticas uniformes INT32 | No | 2 [100] | ||||||||||||||||||||||

| Número de núcleos tensoriales | No | 8 (1.ª generación) [101] | 0 / 8 [97] (2.a generación) | 4 (3.ª generación) | 4 (4ta generación) | |||||||||||||||||||

| Número de núcleos de trazado de rayos | No | 0 / 1 [97] (1.ª generación) | No | 1 (2da generación) | No | 1 (3.ª generación) | No | |||||||||||||||||

| Número de particiones SM = bloques de procesamiento [102] | 1 | 4 | 2 | 4 | ||||||||||||||||||||

| Número de programadores de warp por partición SM | 1 | 2 | 4 | 1 | ||||||||||||||||||||

| Número máximo de nuevas instrucciones emitidas cada ciclo por un solo programador [103] | 2 [104] | 1 | 2 [105] | 2 | 1 | |||||||||||||||||||

| Tamaño de la memoria unificada para caché de datos y memoria compartida | 16 KiB [106] | 16 KiB [106] | 64 KiB | 128 KiB | 64 KiB SM + 24 KiB L1 (separado) [107] | 96 KiB SM + 24 KiB L1 (separado) [107] | 64 KiB SM + 24 KiB L1 (separado) [107] | 64 KiB SM + 24 KiB L1 (separado) [107] | 96 KiB SM + 24 KiB L1 (separado) [107] | 64 KiB SM + 24 KiB L1 (separado) [107] | 128 KiB | 96 KiB [108] | 192 KiB | 128 KiB | 192 KiB | 128 KiB | 256 KiB | |||||||

| Tamaño de la caché de instrucciones L3 por GPU | 32 KiB [109] | utilizar caché de datos L2 | ||||||||||||||||||||||

| Tamaño de la caché de instrucciones L2 por clúster de procesador de textura (TPC) | 8 KiB | |||||||||||||||||||||||

| Tamaño de caché de instrucciones L1.5 por SM [110] | 4 KiB | 32 KiB | 32 KiB | 48 KiB [111] | 128 KiB | 32 KiB | 128 KiB | ~46 KiB [112] | 128 KiB [113] | |||||||||||||||

| Tamaño de la caché de instrucciones L1 por SM | 8 KiB | 8 KiB | ||||||||||||||||||||||

| Tamaño de la caché de instrucciones L0 por partición SM | solo 1 partición por SM | No | 12 KiB | 16 KiB? [114] | 32 KiB | |||||||||||||||||||

| Ancho de instrucción [115] | Instrucciones de 32 bits e instrucciones de 64 bits [116] | Instrucciones de 64 bits + lógica de control de 64 bits cada 7 instrucciones | Instrucciones de 64 bits + lógica de control de 64 bits cada 3 instrucciones | Lógica de control e instrucción combinada de 128 bits | ||||||||||||||||||||

| Ancho del bus de memoria por partición de memoria en bits | 64 ((G)DDR) | 32 ((G)DDR) | 512 (HBM) | 32 ((G)DDR) | 512 (HBM) | 32 ((G)DDR) | 512 (HBM) | 32 ((G)DDR) | 512 (HBM) | |||||||||||||||

| Caché L2 por partición de memoria | 16 KiB [117] | 32 KiB [117] | 128 KiB | 256 KiB | 1 MB | 512 KiB | 128 KiB | 512 KiB | 256 KiB | 128 KiB | 768 KiB | 64 KiB | 512 KiB | 4 MiB | 512 KiB | 8 MiB [118] | 5 MB | |||||||

| Número de unidades de salida de renderizado (ROP) por partición de memoria (o por GPC en modelos posteriores) | 4 | 8 | 4 | 8 | 16 | 8 | 12 | 8 | 4 | 16 | 2 | 8 | 16 | 16 por GPC | 3 por GPC | 16 por GPC | ||||||||

| Especificaciones de arquitectura | 1.0 | 1.1 | 1.2 | 1.3 | 2.0 | 2.1 | 3.0 | 3.2 | 3.5 | 3.7 | 5.0 | 5.2 | 5.3 | 6.0 | 6.1 | 6.2 | 7.0 | 7.2 | 7.5 | 8.0 | 8.6 | 8.7 | 8.9 | 9.0 |

| Capacidad de cómputo (versión) | ||||||||||||||||||||||||

Para obtener más información, lea la guía de programación Nvidia CUDA. [120]

Usos actuales y futuros de la arquitectura CUDA

- Representación acelerada de gráficos 3D

- Interconversión acelerada de formatos de archivos de vídeo

- Cifrado , descifrado y compresión acelerados

- Bioinformática , p. ej. secuenciación de ADN NGS BarraCUDA [121]

- Cálculos distribuidos, como la predicción de la conformación nativa de las proteínas.

- Simulaciones de análisis médicos, por ejemplo realidad virtual basada en imágenes de tomografías computarizadas y resonancias magnéticas

- Simulaciones físicas, [122] en particular en dinámica de fluidos

- Entrenamiento de redes neuronales en problemas de aprendizaje automático

- Inferencia de modelos de lenguaje amplios

- Reconocimiento facial

- Proyectos informáticos voluntarios , como SETI@home y otros proyectos que utilizan el software BOINC

- Dinámica molecular

- Minería de criptomonedas

- Software de estructura a partir del movimiento (SfM)

Comparación con la competencia

CUDA compite con otras pilas de computación de GPU: Intel OneAPI y AMD ROCm .

Mientras que CUDA de Nvidia es de código cerrado, OneAPI de Intel y ROCm de AMD son de código abierto.

API de Intel One

oneAPI es una iniciativa basada en estándares abiertos, creada para apoyar el desarrollo de software para múltiples arquitecturas de hardware. [123] Las bibliotecas oneAPI deben implementar especificaciones abiertas que son discutidas públicamente por los Grupos de Interés Especial, ofreciendo la posibilidad a cualquier desarrollador u organización de implementar sus propias versiones de las bibliotecas oneAPI. [124] [125]

Originalmente fabricado por Intel, otros adoptantes de hardware incluyen a Fujitsu y Huawei.

Fundación de Aceleración Unificada (UXL)

Unified Acceleration Foundation (UXL) es un nuevo consorcio tecnológico que trabaja en la continuación de la iniciativa OneAPI, con el objetivo de crear un nuevo ecosistema de software acelerador de estándares abiertos, estándares abiertos relacionados y proyectos de especificación a través de grupos de trabajo y grupos de interés especial (SIG). El objetivo es ofrecer alternativas abiertas a CUDA de Nvidia. Las principales empresas detrás de él son Intel, Google, ARM, Qualcomm, Samsung, Imagination y VMware. [126]

ROCM de AMD

ROCm [127] es una pila de software de código abierto para la programación de unidades de procesamiento gráfico (GPU) de Advanced Micro Devices (AMD).

Véase también

- SYCL : un estándar abierto de Khronos Group para programar una variedad de plataformas, incluidas las GPU, con C++ moderno de fuente única , similar a la API de tiempo de ejecución CUDA de nivel superior ( fuente única )

- BrookGPU : el compilador del grupo de gráficos de la Universidad de Stanford

- Programación de matrices

- Computación paralela

- Procesamiento de flujo

- rCUDA : una API para realizar cálculos en computadoras remotas

- Modelado molecular en GPU

- Vulkan : API de computación y gráficos 3D de bajo nivel y alto rendimiento

- OptiX : API de trazado de rayos de NVIDIA

- Binario CUDA (cubin): un tipo de binario fat

- Colección de biblioteca numérica : de NEC para su procesador vectorial

Referencias

- ^ ab Shah, Agam. "Nvidia no está totalmente en contra de que terceros fabriquen chips CUDA". www.theregister.com . Consultado el 25 de abril de 2024 .

- ^ Nvidia. "¿Qué es CUDA?". Nvidia . Consultado el 21 de marzo de 2024 .

- ^ ab Abi-Chahla, Fedy (18 de junio de 2008). "CUDA de Nvidia: ¿el fin de la CPU?". Tom's Hardware . Consultado el 17 de mayo de 2015 .

- ^ Zunitch, Peter (24 de enero de 2018). "CUDA vs. OpenCL vs. OpenGL". Videomaker . Consultado el 16 de septiembre de 2018 .

- ^ "OpenCL". NVIDIA Developer . 2013-04-24 . Consultado el 2019-11-04 .

- ^ "Página de inicio de Nvidia CUDA". 18 de julio de 2017.

- ^ Shimpi, Anand Lal; Wilson, Derek (8 de noviembre de 2006). "GeForce 8800 (G80) de Nvidia: GPU rediseñadas para DirectX 10". AnandTech . Consultado el 16 de mayo de 2015 .

- ^ "Introducción: documentación de nsight-visual-studio-edition 12.6". docs.nvidia.com . Consultado el 10 de octubre de 2024 .

- ^ Witt, Stephen (27 de noviembre de 2023). «Cómo la Nvidia de Jensen Huang está impulsando la revolución de la IA». The New Yorker . ISSN 0028-792X . Consultado el 10 de diciembre de 2023 .

- ^ "Compilador CUDA LLVM". 7 de mayo de 2012.

- ^ Primera demostración de OpenCL en una GPU en YouTube

- ^ Demostración de DirectCompute Ocean ejecutándose en una GPU compatible con CUDA de Nvidia en YouTube

- ^ Vasiliadis, Giorgos; Antonatos, Spiros; Polychronakis, Michalis; Markatos, Evangelos P.; Ioannidis, Sotiris (septiembre de 2008). "Gnort: detección de intrusiones en redes de alto rendimiento mediante procesadores gráficos" (PDF) . Avances recientes en detección de intrusiones . Apuntes de clase en informática. Vol. 5230. págs. 116–134. doi :10.1007/978-3-540-87403-4_7. ISBN 978-3-540-87402-7.

- ^ Schatz, Michael C.; Trapnell, Cole; Delcher, Arthur L.; Varshney, Amitabh (2007). "Alineamiento de secuencias de alto rendimiento utilizando unidades de procesamiento gráfico". BMC Bioinformatics . 8 : 474. doi : 10.1186/1471-2105-8-474 . PMC 2222658 . PMID 18070356.

- ^ "Pyrit – Código de Google".

- ^ "Utilice su GPU Nvidia para realizar cálculos científicos". BOINC. 18 de diciembre de 2008. Archivado desde el original el 28 de diciembre de 2008. Consultado el 8 de agosto de 2017 .

- ^ "Kit de desarrollo de software CUDA de Nvidia (CUDA SDK): notas de la versión 2.0 para MAC OS X". Archivado desde el original el 6 de enero de 2009.

- ^ "CUDA 1.1 – Ahora en Mac OS X". 14 de febrero de 2008. Archivado desde el original el 22 de noviembre de 2008.

- ^ "Se revelan las características de CUDA 11". 14 de mayo de 2020.

- ^ "CUDA Toolkit 11.1 incorpora compatibilidad con GPU GeForce RTX 30 Series y Quadro RTX Series". 23 de septiembre de 2020.

- ^ "Mejora de la asignación de memoria con las nuevas funciones de NVIDIA CUDA 11.2". 16 de diciembre de 2020.

- ^ "Explorando las nuevas características de CUDA 11.3". 16 de abril de 2021.

- ^ Silberstein, Mark; Schuster, Assaf ; Geiger, Dan; Patney, Anjul; Owens, John D. (2008). "Cálculo eficiente de productos de suma en GPU mediante caché administrada por software" (PDF) . Actas de la 22.ª conferencia internacional anual sobre supercomputación: ICS '08 (PDF) . Actas de la 22.ª conferencia internacional anual sobre supercomputación: ICS '08. págs. 309–318. doi :10.1145/1375527.1375572. ISBN 978-1-60558-158-3.

- ^ "CUDA C Programming Guide v8.0" (PDF) . nVidia Developer Zone . Enero de 2017. pág. 19 . Consultado el 22 de marzo de 2017 .

- ^ "NVCC fuerza la compilación de archivos .cu en C++". 29 de noviembre de 2011.

- ^ Whitehead, Nathan; Fit-Florea, Alex. "Precisión y rendimiento: compatibilidad con punto flotante e IEEE 754 para GPU Nvidia" (PDF) . Nvidia . Consultado el 18 de noviembre de 2014 .

- ^ "Productos compatibles con CUDA". Zona CUDA . Nvidia Corporation . Consultado el 3 de noviembre de 2008 .

- ^ "Proyecto Coriander: compilar códigos CUDA en OpenCL y ejecutarlos en cualquier lugar". Phoronix.

- ^ Perkins, Hugh (2017). "cuda-on-cl" (PDF) . IWOCL . Consultado el 8 de agosto de 2017 .

- ^ "hughperkins/coriander: Generar código NVIDIA® CUDA™ para dispositivos OpenCL™ 1.2". GitHub. 6 de mayo de 2019.

- ^ "Documentación CU2CL". chrec.cs.vt.edu .

- ^ "GitHub – vosen/ZLUDA". GitHub .

- ^ Larabel, Michael (12 de febrero de 2024), "AMD financió silenciosamente una implementación de CUDA basada en ROCm: ahora es de código abierto", Phoronix , consultado el 12 de febrero de 2024

- ^ "GitHub – chip-spv/chipStar". GitHub .

- ^ "PyCUDA".

- ^ "pycublas". Archivado desde el original el 20 de abril de 2009. Consultado el 8 de agosto de 2017 .

- ^ "CuPy" . Consultado el 8 de enero de 2020 .

- ^ "Guía de programación de NVIDIA CUDA. Versión 1.0" (PDF) . 23 de junio de 2007.

- ^ "Guía de programación NVIDIA CUDA. Versión 2.1" (PDF) . 8 de diciembre de 2008.

- ^ "Guía de programación de NVIDIA CUDA. Versión 2.2" (PDF) . 2 de abril de 2009.

- ^ "Guía de programación de NVIDIA CUDA. Versión 2.2.1" (PDF) . 26 de mayo de 2009.

- ^ "Guía de programación de NVIDIA CUDA. Versión 2.3.1" (PDF) . 26 de agosto de 2009.

- ^ "Guía de programación NVIDIA CUDA. Versión 3.0" (PDF) . 20 de febrero de 2010.

- ^ "Guía de programación NVIDIA CUDA C. Versión 3.1.1" (PDF) . 21 de julio de 2010.

- ^ "Guía de programación NVIDIA CUDA C. Versión 3.2" (PDF) . 9 de noviembre de 2010.

- ^ "Notas de la versión de CUDA 11.0". NVIDIA Developer .

- ^ "Notas de la versión de CUDA 11.1". NVIDIA Developer .

- ^ "Notas de la versión de CUDA 11.5". NVIDIA Developer .

- ^ "Notas de la versión de CUDA 11.8". NVIDIA Developer .

- ^ "Especificaciones de la NVIDIA Quadro NVS 420". Base de datos de GPU de TechPowerUp . 25 de agosto de 2023.

- ^ Larabel, Michael (29 de marzo de 2017). "NVIDIA lanza compatibilidad con GPU Tegra X2 en Nouveau". Phoronix . Consultado el 8 de agosto de 2017 .

- ^ Especificaciones de Nvidia Xavier en TechPowerUp (preliminares)

- ^ "Bienvenido: documentación de Jetson LinuxDeveloper Guide 34.1".

- ^ "NVIDIA ofrece compatibilidad con GPU Volta de código abierto para su SoC Xavier".

- ^ "Arquitectura NVIDIA Ada Lovelace".

- ^ Análisis de la arquitectura de la GPU Turing mediante microbenchmarking

- ^ "H.1. Características y especificaciones técnicas: Tabla 13. Compatibilidad de funciones por capacidad de cómputo". docs.nvidia.com . Consultado el 23 de septiembre de 2020 .

- ^ "Guía de programación CUDA C++".

- ^ Fusionar-Multiplicar-Agregar, realmente ejecutado, Matriz Densa

- ^ como SASS desde 7.5, como PTX desde 8.0

- ^ "Resumen técnico. Serie NVIDIA Jetson AGX Orin" (PDF) . nvidia.com . Consultado el 5 de septiembre de 2023 .

- ^ "Arquitectura de la GPU NVIDIA Ampere GA102" (PDF) . nvidia.com . Consultado el 5 de septiembre de 2023 .

- ^ Luo, Weile; Fan, Ruibo; Li, Zeyu; Du, Dayou; Wang, Qiang; Chu, Xiaowen (2024). "Evaluación comparativa y análisis de la arquitectura de GPU Nvidia Hopper". arXiv : 2402.13499v1 [cs.AR].

- ^ "Ficha técnica NVIDIA A40" (PDF) . nvidia.com . Consultado el 27 de abril de 2024 .

- ^ "ARQUITECTURA DE LA GPU NVIDIA AMPERE GA102" (PDF) . 27 de abril de 2024.

- ^ "Ficha técnica NVIDIA L40" (PDF) . 27 de abril de 2024.

- ^ En los documentos técnicos, los diagramas cúbicos de Tensor Core representan el ancho de la unidad de producto escalar en la altura (4 FP16 para Volta y Turing, 8 FP16 para A100, 4 FP16 para GA102, 16 FP16 para GH100). Las otras dos dimensiones representan la cantidad de unidades de producto escalar (4x4 = 16 para Volta y Turing, 8x4 = 32 para Ampere y Hopper). Los bloques grises resultantes son las operaciones FMA de FP16 por ciclo. Pascal sin Tensor Core solo se muestra para comparación de velocidad, al igual que Volta V100 con tipos de datos que no son FP16.

- ^ "Informe técnico sobre la arquitectura Turing de NVIDIA" (PDF) . nvidia.com . Consultado el 5 de septiembre de 2023 .

- ^ "GPU NVIDIA Tensor Core" (PDF) . nvidia.com . Consultado el 5 de septiembre de 2023 .

- ^ "Arquitectura NVIDIA Hopper en profundidad". 22 de marzo de 2022.

- ^ forma x tamaño del operando convertido, p. ej. 2 núcleos tensores x 4x4x4xFP16/ciclo = 256 bytes/ciclo

- ^ = producto de las primeras 3 filas de la tabla

- ^ = producto de las 2 filas de la tabla anteriores; forma: p. ej. 8x8x4xFP16 = 512 bytes

- ^ Sun, Wei; Li, Ang; Geng, Tong; Stuijk, Sander; Corporaal, Henk (2023). "Disección de núcleos tensoriales mediante microbenchmarks: latencia, rendimiento y comportamientos numéricos". IEEE Transactions on Parallel and Distributed Systems . 34 (1): 246–261. arXiv : 2206.02874 . doi :10.1109/tpds.2022.3217824. S2CID 249431357.

- ^ "Ejecución de subprocesos paralelos ISA versión 7.7".

- ^ Raihan, Md Aamir; Goli, Negar; Aamodt, Tor (2018). "Modelado de GPU con acelerador de aprendizaje profundo habilitado". arXiv : 1811.08309 [cs.MS].

- ^ "Arquitectura NVIDIA Ada Lovelace".

- ^ forma x tamaño del operando convertido, p. ej. 2 núcleos tensores x 4x4x4xFP16/ciclo = 256 bytes/ciclo

- ^ = producto de las primeras 3 filas de la tabla

- ^ = producto de las 2 filas de la tabla anteriores; forma: p. ej. 8x8x4xFP16 = 512 bytes

- ^ Jia, Zhe; Maggioni, Marco; Smith, Jeffrey; Daniele Paolo Scarpazza (2019). "Disección de la GPU NVidia Turing T4 mediante microbenchmarking". arXiv : 1903.07486 [cs.DC].

- ^ Burgess, John (2019). "RTX ON – La GPU NVIDIA TURING". Simposio IEEE Hot Chips 31 de 2019 (HCS) . págs. 1–27. doi :10.1109/HOTCHIPS.2019.8875651. ISBN 978-1-7281-2089-8.S2CID204822166 .

- ^ Jia, Zhe; Maggioni, Marco; Smith, Jeffrey; Daniele Paolo Scarpazza (2019). "Disección de la GPU NVidia Turing T4 mediante microbenchmarking". arXiv : 1903.07486 [cs.DC].

- ^ Burgess, John (2019). "RTX ON – La GPU NVIDIA TURING". Simposio IEEE Hot Chips 31 de 2019 (HCS) . págs. 1–27. doi :10.1109/HOTCHIPS.2019.8875651. ISBN 978-1-7281-2089-8.S2CID204822166 .

- ^ depende del dispositivo

- ^ "Tegra X1". 9 de enero de 2015.

- ^ Arquitectura de GPU NVIDIA H100 Tensor Core

- ^ H.1. Características y especificaciones técnicas – Tabla 14. Especificaciones técnicas por capacidad de cómputo

- ^ Arquitectura NVIDIA Hopper en profundidad

- ^ solo puede ejecutar 160 instrucciones enteras según la guía de programación

- ^ 128 según [1]. 64 de FP32 + 64 unidades separadas?

- ^ 64 por núcleos FP32 y 64 por núcleos FP32/INT flexibles.

- ^ "Guía de programación CUDA C++".

- ^ 32 carriles FP32 se combinan para formar 16 carriles FP64. Puede ser menor según el modelo.

- ^ solo es compatible con 16 carriles FP32, se combinan para formar 4 carriles FP64

- ^ abcdef depende del modelo

- ^ Velocidad efectiva, probablemente sobre puertos FP32. No hay descripción de núcleos FP64 reales.

- ^ También se puede utilizar para adiciones y comparaciones de números enteros.

- ^ 2 ciclos de reloj/instrucción para cada partición SM Burgess, John (2019). "RTX ON – La GPU NVIDIA TURING". Simposio IEEE Hot Chips 31 de 2019 (HCS) . págs. 1–27. doi :10.1109/HOTCHIPS.2019.8875651. ISBN 978-1-7281-2089-8.S2CID204822166 .

- ^ Durant, Luke; Giroux, Olivier; Harris, Mark; Stam, Nick (10 de mayo de 2017). "Dentro de Volta: la GPU para centros de datos más avanzada del mundo". Blog para desarrolladores de Nvidia .

- ^ Los programadores y despachadores tienen unidades de ejecución dedicadas, a diferencia de Fermi y Kepler.

- ^ El envío puede superponerse simultáneamente, si toma más de un ciclo (cuando hay menos unidades de ejecución que 32/Partición SM)

- ^ ¿ Se pueden emitir simultáneamente tuberías MAD y SFU?

- ^ No más de un planificador puede emitir 2 instrucciones a la vez. El primer planificador está a cargo de los warps con ID impares. El segundo planificador está a cargo de los warps con ID pares.

- ^ abcdef memoria compartida separada, pero L1 incluye caché de textura

- ^ "H.6.1. Arquitectura". docs.nvidia.com . Consultado el 13 de mayo de 2019 .

- ^ "Desmitificando la microarquitectura de la GPU a través de microbenchmarking" (PDF) .

- ^ Jia, Zhe; Maggioni, Marco; Staiger, Benjamín; Scarpazza, Daniele P. (2018). "Disección de la arquitectura de la GPU NVIDIA Volta mediante microbenchmarking". arXiv : 1804.06826 [cs.DC].

- ^ "Tegra X1". 9 de enero de 2015.

- ^ Jia, Zhe; Maggioni, Marco; Smith, Jeffrey; Daniele Paolo Scarpazza (2019). "Disección de la GPU NVidia Turing T4 mediante microbenchmarking". arXiv : 1903.07486 [cs.DC].

- ^ "Disección de la arquitectura de la GPU Ampere a través de microbenchmarking".

- ^ Tenga en cuenta que Jia, Zhe; Maggioni, Marco; Smith, Jeffrey; Daniele Paolo Scarpazza (2019). "Disección de la GPU NVidia Turing T4 mediante microbenchmarking". arXiv : 1903.07486 [cs.DC].no está de acuerdo y afirma que hay 2 KiB de caché de instrucciones L0 por partición SM y 16 KiB de caché de instrucciones L1 por SM

- ^ Jia, Zhe; Maggioni, Marco; Staiger, Benjamín; Scarpazza, Daniele P. (2018). "Disección de la arquitectura de la GPU NVIDIA Volta mediante microbenchmarking". arXiv : 1804.06826 [cs.DC].

- ^ "Código de operación de asfermi". GitHub .

- ^ ab solo para acceso con motor de textura

- ^ 25% deshabilitado en RTX 4090

- ^ "I.7. Compute Capability 8.x". docs.nvidia.com . Consultado el 12 de octubre de 2022 .

- ^ "Apéndice F. Características y especificaciones técnicas" (PDF) . (3,2 MiB) , página 148 de 175 (Versión 5.0 octubre de 2012).

- ^ "Bioinformática CUDA de nVidia: BarraCUDA". BioCentric . 19 de julio de 2019 . Consultado el 15 de octubre de 2019 .

- ^ "Parte V: Simulación de física". NVIDIA Developer . Consultado el 11 de septiembre de 2020 .

- ^ "Modelo de programación oneAPI". oneAPI.io . Consultado el 27 de julio de 2024 .

- ^ "Especificaciones | oneAPI". oneAPI.io . Consultado el 27 de julio de 2024 .

- ^ "Especificación oneAPI — Documentación de la especificación oneAPI 1.3-rev-1". oneapi-spec.uxlfoundation.org . Consultado el 27 de julio de 2024 .

- ^ "Exclusiva: Detrás de la trama para romper el control de Nvidia sobre la IA atacando al software". Reuters . Consultado el 5 de abril de 2024 .

- ^ "Pregunta: ¿Qué significa ROCm? · Problema n.° 1628 · RadeonOpenCompute/ROCm". Github.com . Consultado el 18 de enero de 2022 .

Lectura adicional

- Buck, Ian; Foley, Tim; Horn, Daniel; Sugerman, Jeremy; Fatahalian, Kayvon; Houston, Mike; Hanrahan, Pat (1 de agosto de 2004). "Brook para GPU: computación de flujo en hardware gráfico". ACM Transactions on Graphics . 23 (3): 777–786. doi :10.1145/1015706.1015800. ISSN 0730-0301.

- Nickolls, John; Buck, Ian; Garland, Michael; Skadron, Kevin (1 de marzo de 2008). "Programación paralela escalable con CUDA: ¿es CUDA el modelo de programación paralela que los desarrolladores de aplicaciones han estado esperando?". Queue . 6 (2): 40–53. doi :10.1145/1365490.1365500. ISSN 1542-7730.

Enlaces externos

- Sitio web oficial