Procesador superescalar

Este artículo incluye una lista de referencias generales , pero carece de suficientes citas en línea correspondientes . ( Octubre de 2017 ) |

Un procesador superescalar (o procesador de emisión múltiple [1] ) es una CPU que implementa una forma de paralelismo llamada paralelismo a nivel de instrucción dentro de un solo procesador. [2] A diferencia de un procesador escalar , que puede ejecutar como máximo una sola instrucción por ciclo de reloj, un procesador superescalar puede ejecutar más de una instrucción durante un ciclo de reloj al enviar simultáneamente múltiples instrucciones a diferentes unidades de ejecución en el procesador. Por lo tanto, permite un mayor rendimiento (la cantidad de instrucciones que se pueden ejecutar en una unidad de tiempo) del que sería posible de otra manera a una velocidad de reloj dada . Cada unidad de ejecución no es un procesador separado (o un núcleo si el procesador es un procesador multinúcleo ), sino un recurso de ejecución dentro de una sola CPU, como una unidad lógica aritmética .

Si bien una CPU superescalar normalmente también está segmentada , la ejecución superescalar y segmentada se consideran técnicas de mejora del rendimiento diferentes. La primera (superescalar) ejecuta múltiples instrucciones en paralelo mediante el uso de múltiples unidades de ejecución, mientras que la segunda (secuencia segmentada) ejecuta múltiples instrucciones en la misma unidad de ejecución en paralelo dividiendo la unidad de ejecución en diferentes fases. En la figura "Secuencia segmentada superescalar simple", obtener dos instrucciones al mismo tiempo es superescalar, y obtener las dos siguientes antes de que se haya escrito el primer par es segmentación.

La técnica superescalar se asocia tradicionalmente con varias características identificativas (dentro de una CPU determinada):

- Las instrucciones se emiten desde un flujo de instrucciones secuencial.

- La CPU comprueba dinámicamente las dependencias de datos entre instrucciones en tiempo de ejecución (a diferencia de la comprobación del software en tiempo de compilación )

- La CPU puede ejecutar múltiples instrucciones por ciclo de reloj.

Historia

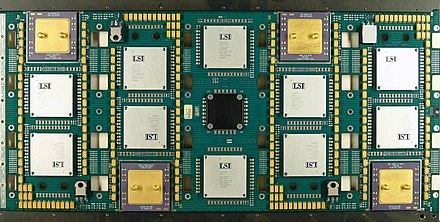

El CDC 6600 de Seymour Cray de 1964 se menciona a menudo como el primer diseño superescalar. El IBM System/360 Model 91 de 1967 fue otro mainframe superescalar. Los microprocesadores Intel i960 CA (1989), [3] el AMD 29000 -series 29050 (1990) y el Motorola MC88110 (1991), [4] fueron los primeros microprocesadores superescalares comerciales de un solo chip. Los microprocesadores RISC como estos fueron los primeros en tener ejecución superescalar, porque las arquitecturas RISC liberan transistores y área de matriz que se puede utilizar para incluir múltiples unidades de ejecución y la uniformidad tradicional del conjunto de instrucciones favorece el despacho superescalar (esta fue la razón por la que los diseños RISC fueron más rápidos que los diseños CISC durante los años 1980 y 1990, y es mucho más complicado hacer un despacho múltiple cuando las instrucciones tienen una longitud de bits variable).

A excepción de las CPU utilizadas en aplicaciones de bajo consumo , sistemas integrados y dispositivos alimentados por batería , esencialmente todas las CPU de propósito general desarrolladas desde aproximadamente 1998 son superescalares.

El P5 Pentium fue el primer procesador x86 superescalar; el Nx586 , el P6 Pentium Pro y el AMD K5 estuvieron entre los primeros diseños que decodificaron instrucciones x86 de forma asincrónica en secuencias de microoperaciones dinámicas similares a microcódigo antes de la ejecución real en una microarquitectura superescalar ; esto abrió la puerta a la programación dinámica de instrucciones parciales almacenadas en búfer y permitió extraer más paralelismo en comparación con los métodos más rígidos utilizados en el más simple P5 Pentium ; también simplificó la ejecución especulativa y permitió frecuencias de reloj más altas en comparación con diseños como el avanzado Cyrix 6x86 .

De escalar a superescalar

Los procesadores más simples son los procesadores escalares. Cada instrucción ejecutada por un procesador escalar generalmente manipula uno o dos elementos de datos a la vez. Por el contrario, cada instrucción ejecutada por un procesador vectorial opera simultáneamente sobre muchos elementos de datos. Una analogía es la diferencia entre la aritmética escalar y la vectorial. Un procesador superescalar es una mezcla de las dos. Cada instrucción procesa un elemento de datos, pero hay múltiples unidades de ejecución dentro de cada CPU, por lo que múltiples instrucciones pueden procesar elementos de datos separados simultáneamente.

El diseño de CPU superescalar enfatiza la mejora de la precisión del despachador de instrucciones y le permite mantener las múltiples unidades de ejecución en uso en todo momento. Esto se ha vuelto cada vez más importante a medida que ha aumentado el número de unidades. Mientras que las primeras CPU superescalares tenían dos ALU y una sola FPU , un diseño posterior como el PowerPC 970 incluye cuatro ALU, dos FPU y dos unidades SIMD. Si el despachador no es efectivo para mantener todas estas unidades alimentadas con instrucciones, el rendimiento del sistema no será mejor que el de un diseño más simple y económico.

Un procesador superescalar suele mantener una tasa de ejecución superior a una instrucción por ciclo de máquina . Pero el simple hecho de procesar varias instrucciones simultáneamente no convierte a una arquitectura en superescalar, ya que las arquitecturas segmentadas , multiprocesador o multinúcleo también lo consiguen, pero con métodos diferentes.

En una CPU superescalar, el despachador lee instrucciones de la memoria y decide cuáles se pueden ejecutar en paralelo, enviando cada una a una de las varias unidades de ejecución contenidas dentro de una sola CPU. Por lo tanto, se puede imaginar que un procesador superescalar tiene múltiples canales paralelos, cada uno de los cuales procesa instrucciones simultáneamente desde un solo hilo de instrucciones.

La mayoría de las CPU superescalares modernas también tienen lógica para reordenar las instrucciones para intentar evitar bloqueos en la canalización y aumentar la ejecución paralela.

Limitaciones

La mejora del rendimiento disponible a partir de técnicas superescalares está limitada por tres áreas clave:

- El grado de paralelismo intrínseco en el flujo de instrucciones (instrucciones que requieren los mismos recursos computacionales de la CPU)

- La complejidad y el costo de tiempo de la lógica de verificación de dependencias y los circuitos de cambio de nombre de registros

- El procesamiento de instrucciones de bifurcación

Los programas binarios ejecutables existentes tienen distintos grados de paralelismo intrínseco. En algunos casos, las instrucciones no dependen unas de otras y pueden ejecutarse simultáneamente. En otros casos, son interdependientes: una instrucción afecta a los recursos o los resultados de la otra. Las instrucciones a = b + c; d = e + fpueden ejecutarse en paralelo porque ninguno de los resultados depende de otros cálculos. Sin embargo, es posible que las instrucciones a = b + c; b = e + fno puedan ejecutarse en paralelo, según el orden en que se completen las instrucciones mientras se desplazan por las unidades.

Aunque el flujo de instrucciones puede no contener dependencias entre instrucciones, una CPU superescalar debe, no obstante, verificar esa posibilidad, ya que no hay garantía de lo contrario y no detectar una dependencia produciría resultados incorrectos.

No importa cuán avanzado sea el proceso de semiconductores o cuán rápida sea la velocidad de conmutación, esto impone un límite práctico a la cantidad de instrucciones que se pueden enviar simultáneamente. Si bien los avances en el proceso permitirán cantidades cada vez mayores de unidades de ejecución (por ejemplo, ALU), la carga de verificar las dependencias de las instrucciones crece rápidamente, al igual que la complejidad de los circuitos de cambio de nombre de registros para mitigar algunas dependencias. En conjunto, el consumo de energía , la complejidad y los costos de retardo de compuerta limitan la aceleración superescalar alcanzable.

Sin embargo, incluso si se utiliza una lógica de comprobación de dependencias infinitamente rápida en una CPU superescalar convencional, si el flujo de instrucciones en sí tiene muchas dependencias, esto también limitaría la posible aceleración. Por lo tanto, el grado de paralelismo intrínseco en el flujo de código constituye una segunda limitación.

Alternativas

En conjunto, estos límites impulsan la investigación de cambios arquitectónicos alternativos, como palabras de instrucción muy largas (VLIW), computación de instrucciones explícitamente paralelas (EPIC), subprocesamiento múltiple simultáneo (SMT) y computación multinúcleo .

Con VLIW, se elimina la engorrosa tarea de verificación de dependencias por parte de la lógica de hardware en tiempo de ejecución y se delega al compilador . La computación de instrucciones explícitamente paralelas (EPIC) es como VLIW con instrucciones de precarga de caché adicionales.

El subprocesamiento simultáneo de múltiples hilos (SMT) es una técnica para mejorar la eficiencia general de los procesadores superescalares. El SMT permite múltiples subprocesos de ejecución independientes para utilizar mejor los recursos que ofrecen las arquitecturas de procesadores modernas. El hecho de que sean independientes significa que sabemos que la instrucción de un subproceso se puede ejecutar fuera de orden y/o en paralelo con la instrucción de otro subproceso. Además, un subproceso independiente no producirá una burbuja de flujo de trabajo en el flujo de código de otro subproceso, por ejemplo, debido a una bifurcación.

Los procesadores superescalares se diferencian de los procesadores multinúcleo en que las distintas unidades de ejecución no son procesadores completos. Un solo procesador se compone de unidades de ejecución de grano más fino, como la ALU , el multiplicador de enteros , el desplazador de enteros, la FPU , etc. Puede haber varias versiones de cada unidad de ejecución para permitir la ejecución de muchas instrucciones en paralelo. Esto difiere de un procesador multinúcleo que procesa simultáneamente instrucciones de varios subprocesos, un subproceso por unidad de procesamiento (llamado "núcleo"). También difiere de un procesador segmentado , donde las múltiples instrucciones pueden estar simultáneamente en varias etapas de ejecución, al estilo de una cadena de montaje .

Las distintas técnicas alternativas no son mutuamente excluyentes: pueden combinarse (y con frecuencia lo hacen) en un único procesador. Por lo tanto, es posible una CPU multinúcleo en la que cada núcleo es un procesador independiente que contiene múltiples canales paralelos, cada uno de los cuales es superescalar. Algunos procesadores también incluyen capacidad vectorial .

Véase también

- Ejecución ansiosa

- Hiperprocesamiento

- Subprocesamiento múltiple simultáneo

- Ejecución fuera de orden

- Estantería de amortiguación

- Ejecución especulativa

- Bloqueo de software , un problema de multiprocesador similar a las dependencias lógicas en superescalares

- Super-threading

Referencias

- ^ P. Pacheco, Introducción a la programación paralela , 2011, sección 2.2.5, "Hay dos enfoques principales para ILP: segmentación... y problemas múltiples... A veces se dice que un procesador que admite problemas múltiples dinámicos es superescalar". A. Chien , Arquitectura informática para científicos , 2022, página 102, "problema múltiple (también conocido como superescalar)".

- ^ "¿Qué es un procesador superescalar? - Definición de Techopedia". Techopedia.com . Consultado el 29 de agosto de 2022 .

- ^ McGeady, Steven (primavera de 1990). "La implementación SuperScalar i960CA de la arquitectura 80960". Compendio de artículos Compcon Spring '90. Trigésima quinta conferencia internacional de la IEEE Computer Society sobre apalancamiento intelectual . págs. 232–240. doi :10.1109/CMPCON.1990.63681. ISBN 0-8186-2028-5.S2CID13206773 .

{{cite book}}:|journal=ignorado ( ayuda ) - ^ Diefendorff, K.; Allen, M. (primavera de 1992). "El microprocesador RISC superescalar Motorola 88110". Compendio de artículos COMPCON primavera de 1992. págs. 157-162. doi :10.1109/CMPCON.1992.186702. ISBN 0-8186-2655-0. Número de identificación del sujeto 34913907.

{{cite book}}:|journal=ignorado ( ayuda )

- Mike Johnson , Diseño de microprocesadores superescalares , Prentice-Hall, 1991, ISBN 0-13-875634-1

- Sorin Cotofana, Stamatis Vassiliadis, "Sobre la complejidad del diseño de la lógica de problemas de las máquinas superescalares", EUROMICRO 1998: 10277-10284

- Steven McGeady , et al., "Mejoras del rendimiento en el microprocesador integrado superescalar i960MM", Actas de la Conferencia de Arquitectura de Computadoras de 1991 (Compcon) , ACM, 1991, págs. 4-7

Enlaces externos

- Ejecución entusiasta / Camino doble / Camino múltiple, por Mark Smotherman