Sistema en un chip

Un sistema en un chip o sistema en chip ( SoC / ˌ ˈ ɛ s oʊ s iː / ; pl. SoCs / ˌ ˈ ɛ s oʊ s iː z / ) es un circuito integrado que integra la mayoría o todos los componentes de una computadora u otro sistema electrónico . Estos componentes casi siempre incluyen una unidad central de procesamiento (CPU) en chip , interfaces de memoria , dispositivos e interfaces de entrada/salida e interfaces de almacenamiento secundario , a menudo junto con otros componentes como módems de radio y una unidad de procesamiento de gráficos (GPU), todo en un solo sustrato o microchip. [1] Los SoC pueden contener funciones de procesamiento de señales digitales y también analógicas , de señal mixta y, a menudo, de radiofrecuencia (de lo contrario, pueden considerarse en un procesador de aplicación discreto).

Los SoC de mayor rendimiento suelen combinarse con chips de memoria y almacenamiento secundario dedicados y físicamente separados (como LPDDR y eUFS o eMMC , respectivamente), que pueden colocarse en capas sobre el SoC en lo que se conoce como una configuración de paquete sobre paquete (PoP), o colocarse cerca del SoC. Además, los SoC pueden utilizar módems inalámbricos separados (especialmente módems WWAN ). [2]

Un SoC integra un microcontrolador , un microprocesador o quizás varios núcleos de procesador con periféricos como una GPU , módems de radio de red celular y Wi-Fi o uno o más coprocesadores . De manera similar a cómo un microcontrolador integra un microprocesador con circuitos periféricos y memoria, un SoC puede considerarse como la integración de un microcontrolador con periféricos aún más avanzados .

En comparación con una arquitectura multichip, un SoC con funcionalidad equivalente tendrá un consumo de energía reducido , así como un área de chip semiconductor más pequeña . Esto se produce a costa de una menor capacidad de reemplazo de los componentes. Por definición, los diseños de SoC están totalmente o casi totalmente integrados en diferentes módulos de componentes . Por estas razones, ha habido una tendencia general hacia una integración más estrecha de los componentes en la industria del hardware informático , en parte debido a la influencia de los SoC y las lecciones aprendidas de los mercados de la informática móvil e integrada.

Los SoC son muy comunes en los mercados de computación móvil (como en dispositivos inteligentes como teléfonos inteligentes y tabletas ) y computación de borde . [3] [4]

Tipos

En general, se pueden distinguir tres tipos de SoC:

- SoC construidos alrededor de un microcontrolador ,

- SoCs construidos alrededor de un microprocesador , que a menudo se encuentran en los teléfonos móviles;

- SoCs de circuitos integrados (SoC) especializados para aplicaciones específicas, diseñados para aplicaciones específicas que no encajan en las dos categorías anteriores.

Aplicaciones

Los SoC se pueden aplicar a cualquier tarea informática, pero normalmente se utilizan en dispositivos móviles como tabletas, teléfonos inteligentes, relojes inteligentes y netbooks, así como en sistemas integrados y en aplicaciones en las que antes se utilizaban microcontroladores .

Sistemas embebidos

Donde antes solo se podían utilizar microcontroladores, los SoC están ganando protagonismo en el mercado de sistemas integrados. Una integración más estrecha del sistema ofrece una mejor confiabilidad y un tiempo medio entre fallas , y los SoC ofrecen una funcionalidad y una potencia informática más avanzadas que los microcontroladores. [5] Las aplicaciones incluyen aceleración de IA , visión artificial integrada , [6] recopilación de datos , telemetría , procesamiento de vectores e inteligencia ambiental . A menudo, los SoC integrados apuntan a los mercados de Internet de las cosas , multimedia, redes, telecomunicaciones y computación de borde . Algunos ejemplos de SoC para aplicaciones integradas incluyen:

- AMD

- Sistema en chip Zynq 7000

- Zynq UltraScale+ MPSoC

- Módulo RFSoC Zynq UltraScale+

- SoC adaptativo Versal

Computación móvil

Los SoC basados en computación móvil siempre incluyen procesadores, memorias, cachés en chip , capacidades de redes inalámbricas y, a menudo, hardware y firmware de cámaras digitales . Con el aumento de los tamaños de memoria, los SoC de gama alta a menudo no tendrán memoria ni almacenamiento flash y, en su lugar, la memoria y la memoria flash se colocarán justo al lado o encima ( paquete sobre paquete ) del SoC. [7] Algunos ejemplos de SoC de computación móvil incluyen:

- Samsung Electronics : lista , generalmente basada en ARM

- Qualcomm :

- Snapdragon ( lista ), utilizado en muchos teléfonos inteligentes. En 2018, los SoC Snapdragon se usaban como la columna vertebral de las computadoras portátiles con Windows 10 , comercializadas como "PC siempre conectadas". [8] [9]

- MediaTek , generalmente basado en ARM

- Series Dimensity y Kompanio. Procesadores independientes para aplicaciones y tabletas que alimentan dispositivos como Amazon Echo Show

Computadoras personales

En 1992, Acorn Computers produjo la gama de ordenadores personales A3010, A3020 y A4000 con el SoC ARM250. Combinaba el procesador ARM2 original de Acorn con un controlador de memoria (MEMC), un controlador de vídeo (VIDC) y un controlador de E/S (IOC). En los ordenadores Acorn anteriores con procesador ARM , se trataba de cuatro chips independientes. El chip ARM7500 era su SoC de segunda generación, basado en los controladores ARM700, VIDC20 e IOMD, y se utilizó ampliamente en dispositivos integrados como decodificadores, así como en los ordenadores personales Acorn posteriores.

Los fabricantes de tabletas y computadoras portátiles han aprendido lecciones de los sistemas integrados y los mercados de teléfonos inteligentes sobre el consumo reducido de energía, mejor rendimiento y confiabilidad a partir de una integración más estrecha de los módulos de hardware y firmware , y LTE y otras comunicaciones de red inalámbrica integradas en chip ( controladores de interfaz de red integrados ). [10]

Estructura

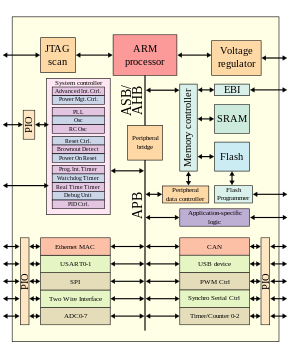

Un SoC consta de unidades funcionales de hardware , incluidos microprocesadores que ejecutan código de software , así como un subsistema de comunicaciones para conectar, controlar, dirigir e interconectar estos módulos funcionales.

Componentes funcionales

Núcleos del procesador

Un SoC debe tener al menos un núcleo de procesador , pero normalmente un SoC tiene más de un núcleo. Los núcleos de procesador pueden ser un microcontrolador , un microprocesador (μP), [11] un procesador de señal digital (DSP) o un procesador de conjunto de instrucciones específicas de la aplicación (ASIP). [12] Los ASIP tienen conjuntos de instrucciones que están personalizados para un dominio de aplicación y diseñados para ser más eficientes que las instrucciones de propósito general para un tipo específico de carga de trabajo. Los SoC multiprocesador tienen más de un núcleo de procesador por definición. La arquitectura ARM es una opción común para los núcleos de procesador SoC porque algunos núcleos de arquitectura ARM son procesadores suaves especificados como núcleos IP . [11]

Memoria

Los SoC deben tener bloques de memoria semiconductores para realizar su cálculo, al igual que los microcontroladores y otros sistemas integrados . Dependiendo de la aplicación, la memoria SoC puede formar una jerarquía de memoria y una jerarquía de caché . En el mercado de la informática móvil, esto es común, pero en muchos microcontroladores integrados de bajo consumo , esto no es necesario. Las tecnologías de memoria para SoC incluyen memoria de solo lectura (ROM), memoria de acceso aleatorio (RAM), ROM programable borrable eléctricamente ( EEPROM ) y memoria flash . [11] Al igual que en otros sistemas informáticos, la RAM se puede subdividir en RAM estática (SRAM) relativamente más rápida pero más cara y la RAM dinámica (DRAM) más lenta pero más barata. Cuando un SoC tiene una jerarquía de caché , la SRAM normalmente se utilizará para implementar los registros del procesador y las cachés integradas de los núcleos , mientras que la DRAM se utilizará para la memoria principal . La "memoria principal" puede ser específica de un solo procesador (que puede ser multinúcleo ) cuando el SoC tiene múltiples procesadores , en este caso es memoria distribuida y debe enviarse a través de la comunicación entre módulos en el chip para que sea accedida por un procesador diferente. [12] Para una discusión más detallada sobre los problemas de memoria de multiprocesamiento, consulte coherencia de caché y latencia de memoria .

Interfaces

Los SoC incluyen interfaces externas , generalmente para protocolos de comunicación . Estos suelen basarse en estándares de la industria como USB , Ethernet , USART , SPI , HDMI , I²C , CSI , etc. Estas interfaces variarán según la aplicación prevista. También pueden ser compatibles los protocolos de redes inalámbricas como Wi-Fi , Bluetooth , 6LoWPAN y comunicación de campo cercano .

Cuando es necesario, los SoC incluyen interfaces analógicas , como convertidores analógico-digitales y digital-analógicos , a menudo para el procesamiento de señales . Estos pueden interactuar con diferentes tipos de sensores o actuadores , incluidos transductores inteligentes . Pueden interactuar con módulos o protectores específicos de la aplicación . [nb 1] O pueden ser internos al SoC, como si un sensor analógico estuviera integrado en el SoC y sus lecturas se debieran convertir en señales digitales para el procesamiento matemático.

Procesadores de señales digitales

Los núcleos de procesador de señal digital (DSP) suelen incluirse en los SoC. Realizan operaciones de procesamiento de señales en SoC para sensores , actuadores , recopilación de datos , análisis de datos y procesamiento multimedia. Los núcleos DSP suelen presentar arquitecturas de conjunto de instrucciones de palabra de instrucción muy larga (VLIW) y de instrucción única, múltiples datos (SIMD) , y por lo tanto son muy aptos para explotar el paralelismo a nivel de instrucción a través del procesamiento paralelo y la ejecución superescalar . [12] : 4 Los núcleos SP suelen presentar instrucciones específicas de la aplicación y, como tales, suelen ser procesadores de conjunto de instrucciones específicas de la aplicación (ASIP). Dichas instrucciones específicas de la aplicación corresponden a unidades funcionales de hardware dedicadas que calculan esas instrucciones.

Las instrucciones DSP típicas incluyen multiplicación-acumulación , transformada rápida de Fourier , multiplicación-suma fusionada y convoluciones .

Otro

Al igual que otros sistemas informáticos, los SoC requieren fuentes de temporización para generar señales de reloj , controlar la ejecución de las funciones del SoC y proporcionar contexto temporal a las aplicaciones de procesamiento de señales del SoC, si es necesario. Las fuentes de tiempo más populares son los osciladores de cristal y los bucles de enganche de fase .

Los periféricos SoC incluyen contadores -temporizadores, temporizadores en tiempo real y generadores de reinicio al encender . Los SoC también incluyen reguladores de voltaje y circuitos de administración de energía .

Comunicación entre módulos

Los SoCs comprenden muchas unidades de ejecución . Estas unidades a menudo deben enviar datos e instrucciones de ida y vuelta. Debido a esto, todos los SoCs, excepto los más triviales, requieren subsistemas de comunicaciones . Originalmente, como con otras tecnologías de microcomputadoras , se usaban arquitecturas de bus de datos , pero recientemente los diseños basados en redes de intercomunicación dispersas conocidas como redes en chip (NoC) han ganado prominencia y se prevé que superen a las arquitecturas de bus para el diseño de SoC en el futuro cercano. [13]

Comunicación basada en bus

Históricamente, un bus informático global compartido conectaba típicamente los diferentes componentes, también llamados "bloques" del SoC. [13] Un bus muy común para las comunicaciones de SoC es el estándar de Arquitectura de Bus de Microcontrolador Avanzado ( AMBA ) libre de regalías de ARM.

Los controladores de acceso directo a memoria enrutan los datos directamente entre las interfaces externas y la memoria del SoC, sin pasar por la CPU o la unidad de control , lo que aumenta el rendimiento de los datos del SoC. Esto es similar a algunos controladores de dispositivos de periféricos en arquitecturas de PC con módulos multichip basados en componentes .

El retraso del cable no es escalable debido a la miniaturización continua , el rendimiento del sistema no se escala con la cantidad de núcleos conectados, la frecuencia operativa del SoC debe disminuir con cada núcleo adicional conectado para que la energía sea sostenible y los cables largos consumen grandes cantidades de energía eléctrica. Estos desafíos son prohibitivos para soportar sistemas de muchos núcleos en un chip. [13] : xiii

Red en un chip

A finales de la década de 2010, surgió una tendencia a que los SoC implementen subsistemas de comunicaciones en términos de una topología similar a una red en lugar de protocolos basados en bus . La tendencia hacia más núcleos de procesador en los SoC ha hecho que la eficiencia de la comunicación en el chip se convierta en uno de los factores clave para determinar el rendimiento y el costo generales del sistema. [13] : xiii Esto ha llevado al surgimiento de redes de interconexión con conmutación de paquetes basada en enrutadores conocidas como " redes en chip " (NoC) para superar los cuellos de botella de las redes basadas en bus. [13] : xiii

Las redes en chip tienen ventajas que incluyen enrutamiento específico de destino y aplicación , mayor eficiencia energética y menor posibilidad de contención de bus . Las arquitecturas de red en chip se inspiran en protocolos de comunicación como TCP y el conjunto de protocolos de Internet para comunicación en chip, [13] aunque normalmente tienen menos capas de red . Las arquitecturas de red en chip óptimas son un área en curso de mucho interés de investigación. Las arquitecturas NoC varían desde topologías de red de computación distribuida tradicionales como toro , hipercubo , mallas y redes de árbol hasta programación de algoritmos genéticos y algoritmos aleatorios como paseos aleatorios con ramificación y tiempo de vida (TTL) aleatorio .

Muchos investigadores de SoC consideran que las arquitecturas NoC son el futuro del diseño de SoC porque se ha demostrado que satisfacen de manera eficiente las necesidades de potencia y rendimiento de los diseños de SoC. Las arquitecturas NoC actuales son bidimensionales. El diseño de circuitos integrados 2D tiene opciones de planificación limitadas a medida que aumenta el número de núcleos en los SoC, por lo que, a medida que surgen los circuitos integrados tridimensionales (3DIC), los diseñadores de SoC buscan construir redes tridimensionales en chip conocidas como 3DNoC. [13]

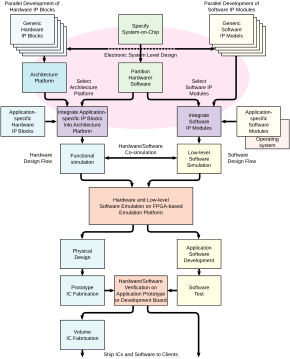

Flujo de diseño

Esta sección necesita citas adicionales para su verificación . ( Marzo de 2017 ) |

Un sistema en un chip consta tanto del hardware , descrito en el apartado Estructura, como del software que controla los núcleos, periféricos e interfaces del microcontrolador, microprocesador o procesador de señales digitales. El flujo de diseño de un SoC tiene como objetivo desarrollar este hardware y software al mismo tiempo, lo que también se conoce como codiseño arquitectónico. El flujo de diseño también debe tener en cuenta las optimizaciones (§ Objetivos de optimización) y las limitaciones.

La mayoría de los SoC se desarrollan a partir de especificaciones de núcleo de propiedad intelectual de componentes de hardware precalificadas para los elementos de hardware y las unidades de ejecución , colectivamente "bloques", descritos anteriormente, junto con controladores de dispositivos de software que pueden controlar su funcionamiento. De particular importancia son las pilas de protocolos que controlan las interfaces estándar de la industria como USB . Los bloques de hardware se ensamblan utilizando herramientas de diseño asistido por computadora , específicamente herramientas de automatización de diseño electrónico ; los módulos de software se integran utilizando un entorno de desarrollo integrado de software .

Los componentes de SoC también suelen diseñarse en lenguajes de programación de alto nivel como C++ , MATLAB o SystemC y convertirse en diseños RTL a través de herramientas de síntesis de alto nivel (HLS) como C a HDL o flow a HDL . [14] Los productos HLS llamados "síntesis algorítmica" permiten a los diseñadores utilizar C++ para modelar y sintetizar niveles de sistema, circuito, software y verificación, todo en un lenguaje de alto nivel comúnmente conocido por los ingenieros informáticos de una manera independiente de las escalas de tiempo, que normalmente se especifican en HDL. [15] Otros componentes pueden seguir siendo software y compilarse e integrarse en procesadores de núcleo blando incluidos en el SoC como módulos en HDL como núcleos IP .

Una vez definida la arquitectura del SoC, todos los elementos de hardware nuevos se escriben en un lenguaje de descripción de hardware abstracto denominado nivel de transferencia de registros (RTL), que define el comportamiento del circuito, o se sintetizan en RTL a partir de un lenguaje de alto nivel mediante síntesis de alto nivel. Estos elementos se conectan entre sí en un lenguaje de descripción de hardware para crear el diseño completo del SoC. La lógica especificada para conectar estos componentes y convertir entre posibles interfaces diferentes proporcionadas por diferentes proveedores se denomina lógica de unión .

Verificación del diseño

Los chips se verifican para comprobar que cumplen con los requisitos de validación antes de enviarlos a una fundición de semiconductores . Este proceso se denomina verificación funcional y representa una parte importante del tiempo y la energía que se gastan en el ciclo de vida del diseño del chip , que a menudo se cita como un 70 %. [16] [17] Con la creciente complejidad de los chips, se están utilizando lenguajes de verificación de hardware como SystemVerilog , SystemC , e y OpenVera. Los errores que se encuentran en la etapa de verificación se informan al diseñador.

Tradicionalmente, los ingenieros han empleado la aceleración de la simulación, la emulación o la creación de prototipos en hardware reprogramable para verificar y depurar hardware y software para diseños de SoC antes de la finalización del diseño, conocido como tape-out . Las matrices de puertas programables en campo (FPGA) son las preferidas para la creación de prototipos de SoC porque los prototipos de FPGA son reprogramables, permiten la depuración y son más flexibles que los circuitos integrados específicos de la aplicación (ASIC). [18] [19]

Con una gran capacidad y un tiempo de compilación rápido, la aceleración de la simulación y la emulación son tecnologías potentes que proporcionan una amplia visibilidad de los sistemas. Sin embargo, ambas tecnologías funcionan lentamente, en el orden de los MHz, lo que puede ser significativamente más lento (hasta 100 veces más lento) que la frecuencia operativa del SoC. Las cajas de aceleración y emulación también son muy grandes y costosas (cuesta más de un millón de dólares). [ cita requerida ]

Los prototipos FPGA, por el contrario, utilizan FPGAs directamente para permitir a los ingenieros validar y probar en, o cerca de, la frecuencia operativa completa de un sistema con estímulos del mundo real. Se utilizan herramientas como Certus [20] para insertar sondas en el RTL del FPGA que hacen que las señales estén disponibles para la observación. Esto se utiliza para depurar interacciones de hardware, firmware y software en múltiples FPGAs con capacidades similares a las de un analizador lógico.

En paralelo, los elementos de hardware se agrupan y pasan a través de un proceso de síntesis lógica , durante el cual se aplican restricciones de rendimiento, como la frecuencia operativa y los retrasos de señal esperados. Esto genera una salida conocida como lista de conexiones que describe el diseño como un circuito físico y sus interconexiones. Estas listas de conexiones se combinan con la lógica de unión que conecta los componentes para producir la descripción esquemática del SoC como un circuito que se puede imprimir en un chip. Este proceso se conoce como colocación y ruta y precede al proceso de salida en el caso de que los SoC se produzcan como circuitos integrados específicos de la aplicación (ASIC).

Objetivos de optimización

Los SoC deben optimizar el uso de energía , el área en la matriz , la comunicación, el posicionamiento para la localidad entre unidades modulares y otros factores. La optimización es necesariamente un objetivo de diseño de los SoC. Si la optimización no fuera necesaria, los ingenieros utilizarían una arquitectura de módulo de múltiples chips sin tener en cuenta el uso del área, el consumo de energía o el rendimiento del sistema en la misma medida.

A continuación se presentan los objetivos de optimización más comunes para los diseños de SoC, con explicaciones de cada uno de ellos. En general, optimizar cualquiera de estas cantidades puede ser un problema de optimización combinatoria difícil y, de hecho, puede ser NP-hard con bastante facilidad. Por lo tanto, a menudo se requieren algoritmos de optimización sofisticados y puede ser práctico utilizar algoritmos de aproximación o heurísticas en algunos casos. Además, la mayoría de los diseños de SoC contienen múltiples variables para optimizar simultáneamente , por lo que se buscan soluciones eficientes en el sentido de Pareto en el diseño de SoC. A menudo, los objetivos de optimizar algunas de estas cantidades son directamente contradictorios, lo que agrega más complejidad a la optimización del diseño de los SoC e introduce compensaciones en el diseño del sistema.

Para una cobertura más amplia de las compensaciones y el análisis de requisitos , consulte ingeniería de requisitos .

Objetivos

Consumo de energía

Los SoC están optimizados para minimizar la energía eléctrica utilizada para realizar las funciones del SoC. La mayoría de los SoC deben usar poca energía. Los sistemas SoC a menudo requieren una batería de larga duración (como los teléfonos inteligentes ), pueden pasar potencialmente meses o años sin una fuente de energía mientras necesitan mantener una función autónoma y, a menudo, están limitados en el uso de energía por una gran cantidad de SoC integrados que se conectan en red en un área. Además, los costos de energía pueden ser altos y la conservación de energía reducirá el costo total de propiedad del SoC. Finalmente, el calor residual del alto consumo de energía puede dañar otros componentes del circuito si se disipa demasiado calor, lo que da otra razón pragmática para conservar energía. La cantidad de energía utilizada en un circuito es la integral de la energía consumida con respecto al tiempo, y la tasa promedio de consumo de energía es el producto de la corriente por el voltaje . Equivalentemente, por la ley de Ohm , la potencia es la corriente al cuadrado por la resistencia o el voltaje al cuadrado dividido por la resistencia :

Los SoCs se integran frecuentemente en dispositivos portátiles como teléfonos inteligentes , dispositivos de navegación GPS , relojes digitales (incluidos los relojes inteligentes ) y netbooks . Los clientes quieren baterías de larga duración para los dispositivos informáticos móviles , otra razón por la que el consumo de energía debe minimizarse en los SoCs. Las aplicaciones multimedia se ejecutan a menudo en estos dispositivos, incluidos los videojuegos, la transmisión de video y el procesamiento de imágenes ; todos los cuales han crecido en complejidad computacional en los últimos años con las demandas de los usuarios y las expectativas de multimedia de mayor calidad . La computación es más exigente a medida que las expectativas se mueven hacia el video 3D a alta resolución con múltiples estándares , por lo que los SoC que realizan tareas multimedia deben ser una plataforma computacionalmente capaz y al mismo tiempo de bajo consumo para funcionar con una batería móvil estándar. [12] : 3

Rendimiento por vatio

Los SoC están optimizados para maximizar la eficiencia energética en el rendimiento por vatio: maximizar el rendimiento del SoC dado un presupuesto de uso de energía. Muchas aplicaciones, como la informática de borde , el procesamiento distribuido y la inteligencia ambiental, requieren un cierto nivel de rendimiento computacional , pero la energía es limitada en la mayoría de los entornos de SoC.

Calor residual

Los diseños de SoC están optimizados para minimizar la salida de calor residual en el chip. Al igual que con otros circuitos integrados , el calor generado debido a la alta densidad de potencia es el cuello de botella para una mayor miniaturización de los componentes. [21] : 1 Las densidades de potencia de los circuitos integrados de alta velocidad, en particular los microprocesadores e incluidos los SoC, se han vuelto muy desiguales. Demasiado calor residual puede dañar los circuitos y erosionar la confiabilidad del circuito con el tiempo. Las altas temperaturas y el estrés térmico afectan negativamente la confiabilidad, la migración de tensión , la disminución del tiempo medio entre fallas , la electromigración , la unión por cable , la metaestabilidad y otra degradación del rendimiento del SoC con el tiempo. [21] : 2–9

En particular, la mayoría de los SoC se encuentran en un área física o volumen pequeño y, por lo tanto, los efectos del calor residual se agravan porque hay poco espacio para que se difunda fuera del sistema. Debido a la gran cantidad de transistores en los dispositivos modernos, a menudo es físicamente posible lograr un diseño con suficiente rendimiento y alta densidad de transistores a partir de procesos de fabricación , pero daría como resultado cantidades inaceptablemente altas de calor en el volumen del circuito. [21] : 1

Estos efectos térmicos obligan a los diseñadores de SoC y otros chips a aplicar márgenes de diseño conservadores , creando dispositivos de menor rendimiento para mitigar el riesgo de fallas catastróficas . Debido al aumento de las densidades de transistores a medida que las escalas de longitud se hacen más pequeñas, cada generación de proceso produce más salida de calor que la anterior. Para agravar este problema, las arquitecturas de SoC suelen ser heterogéneas, lo que crea flujos de calor espacialmente no homogéneos , que no se pueden mitigar de manera efectiva con un enfriamiento pasivo uniforme . [21] : 1

Rendimiento

![[icono]](http://upload.wikimedia.org/wikipedia/commons/thumb/1/1c/Wiki_letter_w_cropped.svg/20px-Wiki_letter_w_cropped.svg.png) | Esta sección necesita ser ampliada . Puedes ayudar agregándole algo. ( Octubre de 2018 ) |

Los SoC están optimizados para maximizar el rendimiento computacional y de comunicaciones .

Estado latente

![[icono]](http://upload.wikimedia.org/wikipedia/commons/thumb/1/1c/Wiki_letter_w_cropped.svg/20px-Wiki_letter_w_cropped.svg.png) | Esta sección necesita ser ampliada . Puedes ayudar agregándole algo. ( Octubre de 2018 ) |

Los SoC están optimizados para minimizar la latencia de algunas o todas sus funciones. Esto se puede lograr al disponer los elementos con la proximidad y la ubicación adecuadas entre sí para minimizar los retrasos de interconexión y maximizar la velocidad a la que se comunican los datos entre módulos, unidades funcionales y memorias. En general, optimizar para minimizar la latencia es un problema NP-completo equivalente al problema de satisfacibilidad booleano .

En el caso de las tareas que se ejecutan en núcleos de procesador, la latencia y el rendimiento se pueden mejorar con la programación de tareas . Sin embargo, algunas tareas se ejecutan en unidades de hardware específicas de la aplicación, e incluso la programación de tareas puede no ser suficiente para optimizar todas las tareas basadas en software a fin de cumplir con las limitaciones de tiempo y rendimiento.

Metodologías

Esta sección necesita ser ampliada . Puedes ayudar agregándole algo. ( Octubre de 2018 ) |

Los sistemas en chip se modelan con técnicas estándar de verificación y validación de hardware , pero se utilizan técnicas adicionales para modelar y optimizar las alternativas de diseño de SoC para que el sistema sea óptimo con respecto al análisis de decisiones de múltiples criterios sobre los objetivos de optimización anteriores.

Programación de tareas

La programación de tareas es una actividad importante en cualquier sistema informático con múltiples procesos o subprocesos que comparten un único núcleo de procesador. Es importante reducir la latencia y aumentar el rendimiento del software integrado que se ejecuta en los núcleos de procesador de un SoC. No todas las actividades informáticas importantes en un SoC se realizan en software que se ejecuta en procesadores integrados, pero la programación puede mejorar drásticamente el rendimiento de las tareas basadas en software y otras tareas que involucran recursos compartidos .

El software que se ejecuta en SoC a menudo programa tareas de acuerdo con la programación de red y algoritmos de programación aleatorios .

Canalización

Las tareas de hardware y software suelen canalizarse en el diseño de procesadores . La canalización es un principio importante para la aceleración en la arquitectura informática . Se utilizan con frecuencia en GPU ( canalización de gráficos ) y procesadores RISC (evoluciones de la canalización RISC clásica ), pero también se aplican a tareas específicas de la aplicación, como el procesamiento de señales digitales y las manipulaciones multimedia en el contexto de los SoC. [12]

Modelado probabilístico

Los SoC suelen analizarse mediante modelos probabilísticos , redes de colas y cadenas de Markov . Por ejemplo, la ley de Little permite modelar los estados de los SoC y los buffers de los NoC como procesos de llegada y analizarlos mediante variables aleatorias de Poisson y procesos de Poisson .

Cadenas de Markov

Los SoC suelen modelarse con cadenas de Markov , tanto en variantes de tiempo discreto como de tiempo continuo . El modelado de cadenas de Markov permite el análisis asintótico de la distribución de estado estable de potencia, calor, latencia y otros factores del SoC para permitir que las decisiones de diseño se optimicen para el caso común.

Fabricación

Esta sección necesita citas adicionales para su verificación . ( Marzo de 2017 ) |

Los chips SoC se fabrican normalmente utilizando tecnología de semiconductores de óxido de metal (MOS). [22] Las listas de red descritas anteriormente se utilizan como base para el flujo de diseño físico ( lugar y ruta ) para convertir la intención de los diseñadores en el diseño del SoC. A lo largo de este proceso de conversión, el diseño se analiza con modelado de tiempo estático, simulación y otras herramientas para garantizar que cumple con los parámetros operativos especificados, como frecuencia, consumo y disipación de energía, integridad funcional (como se describe en el código de nivel de transferencia de registro) e integridad eléctrica.

Una vez corregidos todos los errores conocidos y verificados nuevamente, y realizadas todas las comprobaciones de diseño físico, los archivos de diseño físico que describen cada capa del chip se envían al taller de máscaras de la fundición, donde se grabará un conjunto completo de máscaras litográficas de vidrio. Estas se envían a una planta de fabricación de obleas para crear los dados del SoC antes del empaquetado y la prueba.

Los SoC se pueden fabricar mediante varias tecnologías, entre ellas:

Los ASIC consumen menos energía y son más rápidos que los FPGA, pero no se pueden reprogramar y su fabricación es costosa. Los diseños FPGA son más adecuados para diseños de menor volumen, pero después de suficientes unidades de producción, los ASIC reducen el costo total de propiedad. [23]

Los diseños SoC consumen menos energía y tienen un coste menor y una fiabilidad mayor que los sistemas multichip a los que sustituyen. Al haber menos paquetes en el sistema, también se reducen los costes de montaje.

Sin embargo, como ocurre con la mayoría de los diseños de integración a muy gran escala (VLSI), el coste total [ aclaración necesaria ] es mayor para un chip grande que para la misma funcionalidad distribuida en varios chips más pequeños, debido a los menores rendimientos [ aclaración necesaria ] y a los mayores costes de ingeniería no recurrentes .

Cuando no es factible construir un SoC para una aplicación particular, una alternativa es un sistema en paquete (SiP) que comprende una serie de chips en un solo paquete . Cuando se produce en grandes volúmenes, el SoC es más rentable que el SiP porque su empaquetamiento es más simple. [24] Otra razón por la que se puede preferir el SiP es que el calor residual puede ser demasiado alto en un SoC para un propósito determinado porque los componentes funcionales están demasiado juntos, y en un SiP el calor se disipará mejor de los diferentes módulos funcionales ya que están físicamente más separados.

Ejemplos

Algunos ejemplos de sistemas en un chip son:

- Serie A de Apple

- Procesador de celdas

- La arquitectura de la Epifanía de Adapteva

- Escala ultra fina Xilinx Zynq

- Qualcomm Snapdragon

Puntos de referencia

![[icono]](http://upload.wikimedia.org/wikipedia/commons/thumb/1/1c/Wiki_letter_w_cropped.svg/20px-Wiki_letter_w_cropped.svg.png) | Esta sección necesita ser ampliada . Puedes ayudar agregándole algo. ( Octubre de 2018 ) |

La investigación y el desarrollo de SoC a menudo comparan muchas opciones. Se desarrollan puntos de referencia, como COSMIC, [25] para ayudar a dichas evaluaciones.

Véase también

- Chipete

- Lista de proveedores de sistemas en chip

- Validación post-silicio

- Familia de arquitectura ARM

- RISC-V

- Computadora de placa única

- Sistema en un paquete

- Red en un chip

- PSoC de ciprés

- Procesador de conjunto de instrucciones específicas de la aplicación (ASIP)

- Diseño basado en plataformas

- Laboratorio en un chip

- Órgano en un chip en la tecnología biomédica

- Módulo multichip

- Computación paralela

- Co-arquitectura ARM big.LITTLE

- Aceleración de hardware

Notas

- ^ En los sistemas integrados , los "shields" son análogos a las tarjetas de expansión para PC . Suelen colocarse sobre un microcontrolador como Arduino o un ordenador de placa única como Raspberry Pi y funcionan como periféricos para el dispositivo.

Referencias

- ^ Shah, Agam (3 de enero de 2017). "7 deslumbrantes mejoras en los teléfonos inteligentes con el chip Snapdragon 835 de Qualcomm". Network World .

- ^ Amadeo, R. (18 de febrero de 2020). «El Snapdragon X60 de Qualcomm promete módems 5G más pequeños en 2021». Ars Technica . Conde Nast . Consultado el 17 de diciembre de 2023 .

- ^ Pete Bennett, EE Times . "El porqué, el dónde y el qué del diseño de SoC de bajo consumo". 2 de diciembre de 2004. Consultado el 28 de julio de 2015.

- ^ Nolan, Stephen M. "Gestión de energía para el desarrollo de sistemas en chip (SoC) de Internet de las cosas (IoT)". Diseño y reutilización . Consultado el 25 de septiembre de 2018 .

- ^ "¿Es un procesador SOC de un solo chip adecuado para su proyecto integrado?". Integrado . Consultado el 13 de octubre de 2018 .

- ^ "Qualcomm lanza SoC para visión integrada | Imaging and Machine Vision Europe" www.imveurope.com . Consultado el 13 de octubre de 2018 .

- ^ "Desmontaje del Samsung Galaxy S10 y S10e". iFixit . 6 de marzo de 2019.

- ^ "ARM va a por Intel con una nueva hoja de ruta de chips hasta 2020". Windows Central . Consultado el 6 de octubre de 2018 .

- ^ "PC siempre conectadas, portátiles 4G LTE con mayor duración de batería | Windows" www.microsoft.com . Consultado el 6 de octubre de 2018 .

- ^ "Módems celulares LTE, 4G LTE y 5G de clase Gigabit | Qualcomm". Qualcomm . Consultado el 13 de octubre de 2018 .

- ^ abc Furber, Stephen B. (2000). Arquitectura de sistema en chip ARM . Harlow, Inglaterra: Addison-Wesley. ISBN 0-201-67519-6.OCLC 44267964 .

- ^ abcde Haris Javaid; Sri Parameswaran (2014). Sistema multiprocesador en chip segmentado para multimedia . Springer . ISBN 978-3-319-01113-4.OCLC 869378184 .

- ^ abcdefg Kundu, Santanu; Chattopadhyay, Santanu (2014). Red en chip: la próxima generación de integración de sistemas en chip (1.ª ed.). Boca Raton, FL: CRC Press. ISBN 978-1-4665-6527-2.OCLC 895661009 .

- ^ "Mejores prácticas para la creación de prototipos FPGA de algoritmos MATLAB y Simulink". EEJournal . 25 de agosto de 2011 . Consultado el 8 de octubre de 2018 .

- ^ Bowyer, Bryan (5 de febrero de 2005). "El 'por qué' y el 'qué' de la síntesis algorítmica". EE Times . Consultado el 8 de octubre de 2018 .

- ^ EE Times . "¿La verificación es realmente del 70 por ciento?". 14 de junio de 2004. Consultado el 28 de julio de 2015.

- ^ "Diferencia entre verificación y validación". Clase de pruebas de software . 26 de agosto de 2013. Consultado el 30 de abril de 2018. En las entrevistas ,

la mayoría de los entrevistadores hacen preguntas sobre "¿Cuál es la diferencia entre verificación y validación?". Muchas personas usan verificación y validación indistintamente, pero ambas tienen significados diferentes.

- ^ Rittman, Danny (5 de enero de 2006). "Prototipos nanométricos" (PDF) . Tayden Design . Consultado el 7 de octubre de 2018 .

- ^ "Desde el prototipado de FPGA hasta la producción de ASIC estructurada para reducir costos, riesgos y tiempo de uso". Diseño y reutilización . Consultado el 7 de octubre de 2018 .

- ^ Brian Bailey, EE Times. "Tektronix espera revolucionar el prototipado de ASIC". 30 de octubre de 2012. Consultado el 28 de julio de 2015.

- ^ abcd Ogrenci-Memik, Seda (2015). Gestión del calor en circuitos integrados: monitorización y refrigeración en chip y a nivel de sistema . Londres, Reino Unido: The Institution of Engineering and Technology. ISBN 978-1-84919-935-3.OCLC 934678500 .

- ^ Lin, Youn-Long Steve (2007). Cuestiones esenciales en el diseño de SOC: diseño de sistemas complejos en chip. Springer Science & Business Media . pág. 176. ISBN 978-1-4020-5352-8.

- ^ "FPGA vs ASIC: ¿Diferencias entre ellos y cuál usar? – Centro de ayuda de Numato Lab". numato.com . 17 de julio de 2018 . Consultado el 17 de octubre de 2018 .

- ^ EE Times . "El gran debate: SOC vs. SIP". 21 de marzo de 2005. Consultado el 28 de julio de 2015.

- ^ "COSMIC". www.ece.ust.hk. Consultado el 8 de octubre de 2018 .

Lectura adicional

- Badawy, Wael; Jullien, Graham A., eds. (2003). Sistema en chip para aplicaciones en tiempo real. Serie internacional Kluwer en ingeniería y ciencias de la computación, SECS 711. Boston: Kluwer Academic Publishers . ISBN 978-1-4020-7254-3.OCLC 50478525 .465 páginas.

- Furber, Stephen B. (2000). Arquitectura de sistema en chip ARM . Boston: Addison-Wesley. ISBN 0-201-67519-6.

- Kundu, Santanu; Chattopadhyay, Santanu (2014). Red en chip: la próxima generación de integración de sistemas en chip (1.ª ed.). Boca Raton, FL: CRC Press. ISBN 978-1-4665-6527-2.OCLC 895661009 .

Enlaces externos

- SOCC Conferencia anual internacional de SoC del IEEE

- Herramienta de integración de IP y ensamblaje de plataforma SoC gratuita Baya

- Sistemas en chip para aplicaciones integradas, seminario de la Universidad de Auburn en VLSI

- SoC instantáneo SoC para FPGA definido por C++

- MPSoC – Conferencia anual sobre MPSoC

- Simposio anual

![[icono]](http://upload.wikimedia.org/wikipedia/commons/thumb/1/1c/Wiki_letter_w_cropped.svg/44px-Wiki_letter_w_cropped.svg.png)