Extensión de dirección física

This article needs additional citations for verification. (March 2014) |

En informática , la extensión de dirección física ( PAE ), a veces denominada extensión de dirección de página , [1] es una función de gestión de memoria para la arquitectura x86. PAE fue introducida por primera vez por Intel en el Pentium Pro , y más tarde por AMD en el procesador Athlon . [2] Define una jerarquía de tabla de páginas de tres niveles (en lugar de dos), con entradas de tabla de 64 bits cada una en lugar de 32, lo que permite a estas CPU acceder directamente a un espacio de dirección física mayor a 4 gigabytes (2 32 bytes).

La estructura de la tabla de páginas que utilizan las CPU x86-64 cuando funcionan en modo largo amplía aún más la jerarquía de la tabla de páginas a cuatro o más niveles, lo que amplía el espacio de direcciones virtuales, y utiliza bits de direcciones físicas adicionales en todos los niveles de la tabla de páginas, lo que amplía el espacio de direcciones físicas. También utiliza el bit superior de la entrada de la tabla de páginas de 64 bits como un bit de no ejecución o "NX" , lo que indica que no se puede ejecutar código desde la página asociada. La función NX también está disponible en modo protegido cuando estas CPU ejecutan un sistema operativo de 32 bits, siempre que el sistema operativo habilite PAE.

Historia

PAE se implementó por primera vez en el Intel Pentium Pro en 1995, [3] aunque los chipsets que lo acompañaban generalmente carecían de soporte para los bits de dirección adicionales requeridos. [4]

PAE es compatible con los procesadores Pentium Pro, Pentium II , Pentium III y Pentium 4. Los primeros procesadores de la familia Pentium M ("Banias") introducidos en 2003 también son compatibles con PAE; sin embargo, no muestran la bandera de compatibilidad con PAE en su información de CPUID . [5] Esto se solucionó en una revisión posterior del núcleo "Dothan" en 2005. También estaba disponible en procesadores AMD, incluido el AMD Athlon [6] [7] (aunque los chipsets están limitados a direccionamiento de 32 bits [8] ) y modelos de procesadores AMD posteriores.

Cuando AMD definió su extensión de 64 bits de la arquitectura x86 estándar de la industria, AMD64 o x86-64, también mejoraron el sistema de paginación en " modo largo " basado en PAE. [9] Admite direcciones virtuales de 64 bits [10] : 24 (a julio de 2023, [update]se implementan 48 bits en algunos procesadores y 57 bits en otros [10] : 139, 141–143 [11] ), direcciones físicas de 52 bits, [10] : 24 e incluye la funcionalidad de bits NX . Cuando se inicializa el procesador x86-64, se requiere habilitar la función PAE antes de que el procesador cambie del modo heredado al modo largo. [9]

Diseño

Con PAE, la entrada de la tabla de páginas de la arquitectura x86 se amplía de 32 a 64 bits. Esto permite más espacio para la dirección de página física, o campo de "número de marco de página", en la entrada de la tabla de páginas. En las implementaciones iniciales de PAE, el campo de número de marco de página se amplió de 20 a 24 bits. El tamaño del "desplazamiento de bytes" desde la dirección que se está traduciendo sigue siendo de 12 bits, por lo que el tamaño total de la dirección física aumenta de 32 bits a 36 bits (es decir, de 20+12 a 24+12). Esto aumentó la memoria física que teóricamente es direccionable por la CPU de 4 GB a 64 GB.

En los primeros procesadores que admitían PAE, el soporte para direcciones físicas más grandes es evidente en la distribución de pines de su paquete, con designaciones de pines de dirección que llegan hasta A35 en lugar de detenerse en A31. [12] Las familias de procesadores posteriores utilizan interconexiones como Hypertransport o QuickPath Interconnect , que carecen de señales de dirección de memoria dedicadas, por lo que esta relación es menos evidente.

El tamaño de 32 bits de la dirección virtual no se modifica, por lo que el software de aplicación habitual sigue utilizando instrucciones con direcciones de 32 bits y (en un modelo de memoria plana ) está limitado a 4 gigabytes de espacio de dirección virtual. Los sistemas operativos que admiten este modo utilizan tablas de páginas para asignar el espacio de dirección virtual habitual de 4 GB a la memoria física, que, según el sistema operativo y el resto de la plataforma de hardware, puede ser de hasta 64 GB. La asignación se aplica normalmente por separado para cada proceso , de modo que la RAM adicional es útil aunque ningún proceso pueda acceder a toda ella simultáneamente.

El trabajo posterior asociado con el desarrollo de la arquitectura x86-64 de AMD amplió el tamaño teórico posible de las direcciones físicas a 52 bits. [10] : 24

Estructuras de tablas de páginas

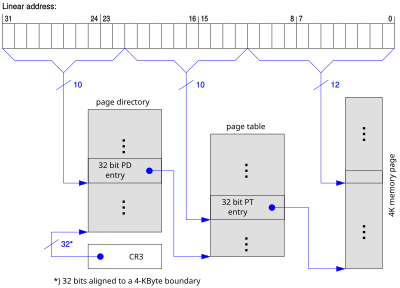

Paginación de 32 bits, páginas de 4 KiB, sin PAE

En modo protegido con paginación habilitada (el bit 31, PG, del registro de control CR0está establecido), pero sin PAE, los procesadores x86 utilizan un esquema de traducción de páginas de dos niveles. El registro de control CR3 contiene la dirección física alineada a la página de un solo directorio de páginas de 4 KB de longitud . Esto se divide en 1024 entradas de directorio de páginas de cuatro bytes que, a su vez, si son válidas, contienen las direcciones físicas alineadas a la página de las tablas de páginas , cada una de 4 KB de tamaño. Estas, de manera similar, consisten en 1024 entradas de tabla de páginas de cuatro bytes que, si son válidas, contienen las direcciones físicas alineadas a la página de páginas de 4 KB de memoria física (RAM).

Paginación de 32 bits, páginas de 4 MiB, sin PAE

Las entradas del directorio de páginas tienen un indicador adicional en el bit 7, denominado PS(para el tamaño de página ). Si el sistema ha establecido este bit en 1, la entrada del directorio de páginas no apunta a una tabla de páginas, sino a una sola página grande de 4 MB ( Extensión de tamaño de página ).

Paginación de 32 bits, páginas de 4 KiB, con PAE

La habilitación de PAE (mediante la configuración del bit 5, PAE, del registro del sistema CR4) provoca cambios importantes en este esquema. De manera predeterminada, el tamaño de cada página permanece en 4 KB. Cada entrada en la tabla de páginas y el directorio de páginas pasa a tener una longitud de 64 bits (8 bytes), en lugar de 32 bits, para permitir bits de dirección adicionales. Sin embargo, el tamaño de cada tabla no cambia, por lo que tanto la tabla como el directorio ahora tienen solo 512 entradas. Debido a que esto permite solo la mitad de las entradas del esquema original, se ha agregado un nivel adicional de jerarquía, por lo que el registro del sistema CR3ahora apunta físicamente a una tabla de punteros de directorio de páginas , una tabla corta que contiene cuatro punteros a directorios de páginas.

El soporte de direcciones de 64 bits en la tabla de páginas es un cambio significativo, ya que permite dos cambios en el direccionamiento del procesador. En primer lugar, el caminador de la tabla de páginas, que utiliza direcciones físicas para acceder a la tabla de páginas y al directorio, ahora puede acceder a direcciones físicas mayores que las direcciones físicas de 32 bits admitidas en sistemas sin PAE. A partir de CR3, el caminador de la tabla de páginas puede acceder a directorios y tablas de páginas que están más allá del rango de 32 bits. En segundo lugar, la dirección física para los datos a los que se accede (almacenados en la tabla de páginas) se puede representar como una dirección física mayor que las direcciones de 32 bits admitidas en un sistema sin PAE. Nuevamente, esto permite que los accesos a los datos accedan a regiones de memoria física más allá del rango de 32 bits. [13]

Paginación de 32 bits, páginas de 2 MiB, con PAE

Las entradas del directorio de páginas tienen un indicador adicional en el bit 7, denominado PS(para el tamaño de página ). Si el sistema ha establecido este bit en 1, la entrada del directorio de páginas no apunta a una tabla de páginas, sino a una sola página grande de 2 MB ( Extensión de tamaño de página ).

Resumen de paginación de 32 bits

En todos los formatos de tabla de páginas compatibles con IA-32 y x86-64 , los 12 bits menos significativos de la entrada de la tabla de páginas son interpretados por la unidad de administración de memoria o están reservados para el uso del sistema operativo. En los procesadores que implementan la función de "no ejecución" o "deshabilitación de ejecución", el bit más significativo (bit 63) es el bit NX . Los siguientes once bits más significativos (bits 52 a 62) están reservados para el uso del sistema operativo por las especificaciones de arquitectura de Intel y AMD. Por lo tanto, de los 64 bits de la entrada de la tabla de páginas, 12 bits de orden bajo y 12 bits de orden alto tienen otros usos, dejando 40 bits (bits 12 a 51) para el número de página física. Combinados con 12 bits de "desplazamiento dentro de la página" desde la dirección lineal, hay un máximo de 52 bits disponibles para direccionar la memoria física. Esto permite una configuración de RAM máxima de 2,52 bytes , o 4 petabytes (aproximadamente 4,5×1015 bytes ).

Paginación x86-64

En los procesadores x86-64 en modo largo nativo , el esquema de traducción de direcciones utiliza PAE pero añade una cuarta tabla, la tabla de nivel 4 de mapa de páginas de 512 entradas , y extiende la tabla de punteros de directorio de páginas a 512 entradas en lugar de las 4 entradas originales que tiene en modo protegido. Esto significa que se traducen 48 bits de número de página virtual, lo que da un espacio de dirección virtual de hasta 256 TB. Para algunos procesadores, se puede habilitar un modo con una quinta tabla, la tabla de nivel 5 de mapa de páginas de 512 entradas ; esto significa que se traducen 57 bits de número de página virtual, lo que da un espacio de dirección virtual de hasta 128 PB. [10] : 141–153 En las entradas de la tabla de páginas, en la especificación original, se implementan 40 bits de número de página física.

Soporte de hardware

El software puede identificar mediante el CPUIDindicador PAEsi una CPU admite el modo PAE o no. Existe un programa gratuito para Microsoft Windows que enumera muchas capacidades del procesador, incluida la compatibilidad con PAE. [14] En Linux, comandos como cat /proc/cpuinfopueden enumerar el paeindicador cuando está presente, [15] así como otras herramientas como la herramienta de detección de hardware SYSLINUX .

Para que el procesador funcione en modo PAE, se requiere que el sistema operativo lo admita. Para utilizar PAE para acceder a más de 4 GB de RAM, se requiere más compatibilidad en el sistema operativo, en el chipset y en la placa base. Algunos chipsets no admiten direcciones de memoria física superiores a 4 GB (FFFFFFFF en hexadecimal) y algunas placas base simplemente no tienen suficientes zócalos de RAM para permitir la instalación de más de 4 GB de RAM. Sin embargo, incluso si no hay más de 4 GB de RAM disponibles y accesibles, una CPU compatible con PAE se puede ejecutar en modo PAE, por ejemplo, para permitir el uso de la función No ejecutar .

Compatibilidad con sistemas operativos

Microsoft Windows

Las versiones de 32 bits de Microsoft Windows admiten PAE si se inician con la opción adecuada. Según Mark Russinovich , miembro técnico de Microsoft , se descubrió que algunos controladores eran inestables cuando se encontraban con direcciones físicas superiores a 4 GB. [16]

La siguiente tabla muestra los límites de memoria para las versiones de 32 bits de Microsoft Windows:

| Versión de Windows | Límite de memoria |

|---|---|

| Windows 2000 Profesional, Servidor | 4 GB |

| Servidor avanzado de Windows 2000 | 8 GB |

| Centro de datos de Windows 2000 | 32 GB |

| Inicio de Windows XP | 0,5 GB |

| Windows XP (otras ediciones) | 4 GB |

| Servidor Web de Windows 2003 SP2 | 2 GB |

| Windows Server 2003 SP2 estándar | 4 GB |

| Windows Server 2003 Enterprise/Datacenter SP2 | 64 GB |

| Servidor de almacenamiento Windows 2003 Enterprise | 8 GB |

| Windows Storage Server 2003 (otras ediciones) | 4 GB |

| Servidor doméstico de Windows | 4 GB |

| Inicio de Windows Vista | 1 GB |

| Windows Vista (otras ediciones) | 4 GB |

| Windows Server 2008 Standard, Web | 4 GB |

| Windows Server 2008 Enterprise, Centro de datos | 64 GB |

| Inicio de Windows 7 | 2 GB |

| Windows 7 (otras ediciones) | 4 GB |

| Windows 8 (todas las ediciones) | 4 GB |

| Windows 10 (todas las ediciones) | 4 GB |

Las versiones originales de Windows XP y Windows XP SP1 usaban el modo PAE para permitir que la RAM se extendiera más allá del límite de direcciones de 4 GB. Sin embargo, esto generó problemas de compatibilidad con controladores de terceros, lo que llevó a Microsoft a eliminar esta capacidad en Windows XP Service Pack 2. Windows XP SP2 y posteriores, de manera predeterminada, en procesadores con la función de no ejecución (NX) o deshabilitación de ejecución (XD) , se ejecuta en modo PAE para permitir NX. [20] El bit NX reside en el bit 63 de la entrada de la tabla de páginas y, sin PAE, las entradas de la tabla de páginas en sistemas de 32 bits tienen solo 32 bits; por lo tanto, se requiere el modo PAE para aprovechar la función NX. Sin embargo, las versiones "cliente" de Windows de 32 bits (Windows XP SP2 y posteriores, Windows Vista, Windows 7) limitan el espacio de direcciones físicas a los primeros 4 GB para la compatibilidad con el controlador [16], aunque estas versiones se ejecutan en modo PAE si está habilitado el soporte NX.

Windows 8 y versiones posteriores solo se ejecutarán en procesadores que admitan PAE, además de NX y SSE2 . [21] [22]

macOS

Desde Mac OS X Tiger hasta Mac OS X Snow Leopard admiten PAE y el bit NX en procesadores IA-32; Snow Leopard fue la última versión que admitió procesadores IA-32. En procesadores x86-64, todas las versiones de macOS utilizan paginación de 4 niveles (paginación IA-32e en lugar de PAE) para direccionar la memoria por encima de los 4 GB. Los sistemas Mac Pro y Xserve pueden utilizar hasta 64 GB de RAM. [23]

Linux

El núcleo Linux incluye soporte completo para el modo PAE a partir de la versión 2.3.23, [24] en 1999, lo que permite el acceso a hasta 64 GB de memoria en máquinas de 32 bits. Un núcleo Linux compatible con PAE requiere que la CPU también sea compatible con PAE. El núcleo Linux admite PAE como una opción de compilación y las principales distribuciones proporcionan un núcleo PAE como opción o como opción predeterminada.

La función de bit NX requiere un kernel creado con soporte PAE. [25]

Las distribuciones Linux ahora usan comúnmente un kernel habilitado para PAE como predeterminado, una tendencia que comenzó en 2009. [26] A partir de 2012 [update], muchas, incluyendo Ubuntu (y derivados como Xubuntu y Linux Mint ), [27] [28] Red Hat Enterprise Linux 6.0, [29] y CentOS , han dejado de distribuir kernels que no sean PAE, lo que hace obligatorio el hardware compatible con PAE. Las distribuciones Linux que requieren PAE pueden negarse a arrancar en procesadores de la familia Pentium M porque no muestran el indicador de compatibilidad con PAE en su información de CPUID (aunque se admita internamente). [5] Sin embargo, esto se puede evitar fácilmente con la forcepaeopción. [30]

Las distribuciones que aún ofrecen una opción no PAE, incluyendo Debian (y derivados como LMDE 2 (Linux Mint Debian Edition) [31] ), Slackware y LXLE , normalmente lo hacen con etiquetas "i386", "i486" o "retro". [32] [33] El artículo Distribución ligera de Linux sí enumera algunas otras, que permiten instalar Linux en computadoras antiguas.

Otros

FreeBSD y NetBSD también admiten PAE como una opción de compilación del núcleo. FreeBSD admite PAE en la serie 4.x a partir de la 4.9, en la serie 5.x a partir de la 5.1 y en todas las versiones 6.x y posteriores. Para que sea compatible, se requiere la PAEopción de configuración del núcleo. Los módulos del núcleo cargables solo se pueden cargar en un núcleo con PAE habilitado si los módulos se compilaron con PAE habilitado; los módulos binarios en las distribuciones de FreeBSD no se compilan con PAE habilitado y, por lo tanto, no se pueden cargar en núcleos con PAE. No todos los controladores admiten más de 4 GB de memoria física; esos controladores no funcionarán correctamente en un sistema con PAE. [34]

OpenBSD ha brindado soporte para PAE desde 2006 con el kernel estándar GENERIC i386. GeNUA mbH brindó soporte para la implementación inicial. [35] Desde la versión 5.0, PAE ha tenido una serie de cambios, en particular cambios en el procesamiento MMU i386 para PMAP, consulte pmap(9). [36] [ verificación fallida ]

Solaris admite PAE a partir de la versión 7 de Solaris. Sin embargo, los controladores de terceros utilizados con la versión 7 que no incluyen específicamente compatibilidad con PAE pueden funcionar de manera errática o fallar directamente en un sistema con PAE. [37]

Haiku agregó soporte inicial para PAE algún tiempo después del lanzamiento de R1 Alpha 2. Con el lanzamiento de R1 Alpha 3, PAE ahora cuenta con soporte oficial.

ArcaOS tiene soporte limitado para PAE con el propósito de crear discos RAM por encima del límite de 4 GB. [38]

Véase también

- Límite de RAM

- Extensión de tamaño de página

- Agujero PCI

- PSE-36

- Arquitectura de Windows NT

- Barrera de 3 GB

- Extensión de dirección física grande (LPAE): en la arquitectura ARM

- Paginación Intel de 5 niveles

Referencias

- ^ Actualización de especificaciones del procesador Intel® Xeon® de doble núcleo a 2,80 GHz (PDF) . Intel Corporation. Octubre de 2006. pág. 18.

- ^ "Apéndice E". Guía de optimización de código del procesador x86 AMD Athlon™ (PDF) (edición de revisión K). AMD, Inc. Febrero de 2002. pág. 250. Consultado el 13 de abril de 2017.

Se utiliza un índice de 2 bits que consta de bits PCD y PWT de la entrada de la tabla de páginas para seleccionar uno de los cuatro campos de registro PAT cuando se habilita PAE (extensiones de dirección de página) o cuando la PDE no describe una página grande.

- ^ T. Shanley (1998). Arquitectura de sistemas Pentium Pro y Pentium II. Addison-Wesley Professional. pág. 439. ISBN 978-0-201-30973-7.

- ^ "Sistemas operativos y soporte PAE". Centro de desarrolladores de hardware . 1 de junio de 2017 . Consultado el 11 de julio de 2023 .

- ^ ab "PAE - Wiki de ayuda de la comunidad de Ubuntu".

- ^ "Apéndice E". Guía de optimización de código del procesador x86 AMD Athlon™ (PDF) (edición de revisión K). AMD, Inc. Febrero de 2002. pág. 250. Consultado el 13 de abril de 2017.

Se utiliza un índice de 2 bits que consta de bits PCD y PWT de la entrada de la tabla de páginas para seleccionar uno de los cuatro campos de registro PAT cuando se habilita PAE (extensiones de dirección de página) o cuando la PDE no describe una página grande.

- ^ "AMD Athlon 500 - AMD-K7500MTR51B C". Cpu-world.com . 26 de marzo de 2014 . Consultado el 11 de julio de 2023 .

- ^ "Controlador del sistema AMD-762" (PDF) . p. 2.

Admite hasta 4 Gbytes de memoria

- ^ ab AMD Corporation (junio de 2023). "Volumen 2: Programación del sistema" (PDF) . Manual del programador de la arquitectura AMD64 . AMD Corporation. pág. 139. Consultado el 11 de julio de 2023.

La traducción de páginas en modo largo requiere el uso de extensiones de dirección física (PAE). Antes de activar el modo largo, se debe habilitar PAE configurando CR4.PAE en 1. Activar el modo largo antes de habilitar PAE hace que se produzca una excepción de protección general (#GP).

- ^ abcde AMD Corporation (junio de 2023). "Volumen 2: Programación del sistema" (PDF) . Manual del programador de la arquitectura AMD64 . AMD Corporation . Consultado el 11 de julio de 2023 .

- ^ "Volumen 3 (3A, 3B, 3C y 3D): Guía de programación del sistema". Manual del desarrollador de software de arquitecturas Intel 64 e IA-32 . Intel. Junio de 2023. págs. 4-7 . Consultado el 11 de julio de 2023 .

- ^ Hoja de datos del procesador Pentium® III Xeon™ a 500 y 550 MHz . Intel Corporation. Febrero de 2000. pág. 86. 245094-002.

A[35:03]# (E/S): Las señales A[35:3]# (Dirección) definen un espacio de dirección de memoria física de 2 a 36 bytes.

- ^ "4.4 Paginación". Manual del desarrollador de software de arquitecturas Intel® 64 e IA-32, volumen 3A. Intel . Consultado el 28 de octubre de 2023 .

- ^ "Coreinfo - Sysinternals". Windows Sysinternals . Microsoft. 7 de junio de 2023 . Consultado el 11 de julio de 2023 .

- ^ "Detectando su hardware". Gentoo. 8 de octubre de 2008. Archivado desde el original el 3 de mayo de 2013. Consultado el 28 de abril de 2013 .

{{cite web}}: CS1 maint: unfit URL (link) - ^ de Mark Russinovich (21 de julio de 2008). "Superando los límites de Windows: memoria física". Archivado desde el original el 25 de julio de 2008. Consultado el 11 de julio de 2010 .

- ^ "Límites de memoria para versiones de Windows". MSDN . Microsoft . 5 de diciembre de 2007. Archivado desde el original el 17 de diciembre de 2007 . Consultado el 16 de noviembre de 2015 .

- ^ "Extensiones de direccionamiento físico (PAE) de Intel en Windows 2000". Soporte . Microsoft . 26 de octubre de 2007. Archivado desde el original el 2008-01-01 . Consultado el 2007-12-29 .

- ^ "Descripción general de Windows Server 2003 R2 Datacenter Edition". TechNet . Microsoft . Archivado desde el original el 28 de noviembre de 2011 . Consultado el 15 de mayo de 2009 .

- ^ "La memoria RAM que indican el cuadro de diálogo Propiedades del sistema y la herramienta Información del sistema es menor de lo esperado en Windows Vista o en Windows XP Service Pack 2 o una versión posterior (MSKB 888137)". Base de conocimiento . Microsoft. Archivado desde el original el 4 de febrero de 2009 . Consultado el 30 de enero de 2009 .

- ^ Khurshid, Usman (2 de noviembre de 2012). "Cómo comprobar si su procesador es compatible con PAE, NX y SSE2 para la instalación de Windows 8". technize.net . Technize . Consultado el 20 de abril de 2014 .

- ^ "Guía de requisitos de compatibilidad de PAE/NX/SSE2 para Windows 8". Microsoft Docs. 10 de febrero de 2014. Consultado el 11 de julio de 2023 .

- ^ "El camino hacia Mac OS X 10.6 Snow Leopard: 64 bits". 26 de septiembre de 2008. Consultado el 26 de septiembre de 2008 .

- ^ Molnar, Ingo (20 de octubre de 1999). "Explicación breve de los cambios en la RAM de 64 GB en x86 2.3.23-pre4 [parche HIGHMEM]". linux-kernel (Lista de correo).

- ^ Mauerer, Wolfgang (11 de marzo de 2010). Arquitectura profesional del kernel de Linux. Figura 3.16 Flujo de código para paging_init. ISBN 978-1-118-07991-1La protección de desactivación de ejecución

también está habilitada si el procesador la admite y si el kernel se compiló con soporte PAE; desafortunadamente, la función no está disponible en otros casos.

- ^ "Especificaciones x86 para Fedora 11". Archivado desde el original el 4 de julio de 2010.

- ^ "Xubuntu 12.04 lanzado". Xubuntu.org . 26 de abril de 2012 . Consultado el 24 de octubre de 2015 .

El kernel no PAE no estará disponible en futuras versiones de Xubuntu.

- ^ "PAE". Wiki de ayuda de la comunidad de Ubuntu . Consultado el 11 de julio de 2023 .

- ^ "Notas de la versión de RHEL 6, 12.6. Actualizaciones generales del kernel 12.6.1. Extensión de dirección física (PAE)". RedHat . Consultado el 27 de noviembre de 2013 .

- ^ "Los parámetros de la línea de comandos del núcleo". La documentación del núcleo de Linux .

- ^ "Problemas conocidos en Linux Mint Debian". Archivado desde el original el 16 de octubre de 2015. Consultado el 24 de octubre de 2015.

Para garantizar la compatibilidad con procesadores que no sean PAE, las versiones de 32 bits de Linux Mint Debian vienen con un núcleo 486 por defecto.

- ^ "Precise Puppy". puppylinux.org . PuppyLinux. Archivado desde el original el 13 de agosto de 2014 . Consultado el 20 de abril de 2014 .

- ^ "2.1. Hardware compatible". Guía de instalación de Debian GNU/Linux . SPI. Archivado desde el original el 13 de mayo de 2014 . Consultado el 20 de abril de 2014 .

- ^ "Página de manual de FreeBSD i386 5.5-RELEASE PAE(4)". 2003-04-08 . Consultado el 2023-07-11 .

- ^ "PAE para OpenBSD/i386 por Michael Shalayeff, NYC". 2006 . Consultado el 3 de febrero de 2018 .

- ^ – Manual del desarrollador del kernel de OpenBSD

- ^ "Compatibilidad añadida con el modo de extensión de dirección física (PAE)". Notas de la versión de Solaris 7 5/99 (Intel Platform Edition), Apéndice B: Lista de compatibilidad de hardware y guía de configuración de dispositivos (Intel Platform Edition) 5/99 . 1999 . Consultado el 23 de marzo de 2018 .

- ^ "ArcaOS 5.0 de Arca Noae es la nueva versión de OS/2 para el siglo XXI". 2017 . Consultado el 16 de diciembre de 2019 .

Lectura adicional

- "Manual del desarrollador de software de arquitecturas Intel 64 e IA-32, volumen 3A: Guía de programación del sistema, parte 1". Intel . 11 de febrero de 2014.

- "Extensión de dirección física". Microsoft Docs . 7 de enero de 2021 . Consultado el 11 de julio de 2023 .