Interconexión Intel QuickPath

Este artículo necesita ser actualizado . ( Enero de 2014 ) |

Intel QuickPath Interconnect ( QPI ) [1] [2] es una interconexión de procesador punto a punto desarrollada por Intel que reemplazó al bus frontal (FSB) en Xeon , Itanium y ciertas plataformas de escritorio a partir de 2008. Aumentó la escalabilidad y el ancho de banda disponible. Antes del anuncio del nombre, Intel se refería a él como Interfaz de sistema común ( CSI ). [3] Las encarnaciones anteriores se conocían como Yet Another Protocol (YAP) y YAP+.

QPI 1.1 es una versión significativamente renovada introducida con Sandy Bridge-EP ( plataforma Romley ). [4]

QPI fue reemplazado por Intel Ultra Path Interconnect (UPI) en los procesadores Skylake -SP Xeon basados en el socket LGA 3647. [5]

Fondo

Aunque a veces se lo denomina "bus", QPI es una interconexión punto a punto. Fue diseñado para competir con HyperTransport , que Advanced Micro Devices (AMD) había utilizado desde aproximadamente 2003. [6] [7] Intel desarrolló QPI en su Centro de Diseño de Microprocesadores de Massachusetts (MMDC) por miembros de lo que había sido el Grupo de Desarrollo Alpha , que Intel había adquirido de Compaq y HP y que a su vez provenía originalmente de Digital Equipment Corporation (DEC). [8] Su desarrollo había sido reportado ya en 2004. [9]

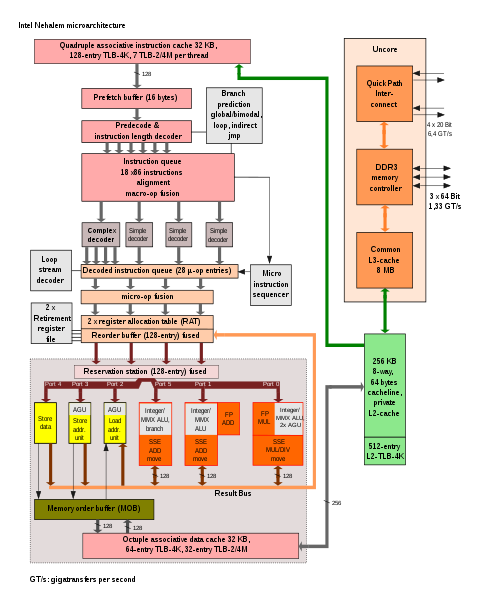

Intel lo lanzó por primera vez para procesadores de escritorio en noviembre de 2008 en el chipset Intel Core i7-9xx y X58 . Se lanzó en procesadores Xeon con nombre en código Nehalem en marzo de 2009 y en procesadores Itanium en febrero de 2010 (con nombre en código Tukwila). [10]

Fue reemplazado por Intel Ultra Path Interconnect a partir de 2017 en las plataformas Xeon Skylake-SP . [11]

Implementación

El QPI es un elemento de una arquitectura de sistema que Intel llama arquitectura QuickPath que implementa lo que Intel llama tecnología QuickPath . [12] En su forma más simple en una placa base de un solo procesador, se utiliza un solo QPI para conectar el procesador al concentrador IO (por ejemplo, para conectar un Intel Core i7 a un X58 ). En instancias más complejas de la arquitectura, pares de enlaces QPI separados conectan uno o más procesadores y uno o más concentradores IO o concentradores de enrutamiento en una red en la placa base, lo que permite que todos los componentes accedan a otros componentes a través de la red. Al igual que con HyperTransport, la arquitectura QuickPath asume que los procesadores tendrán controladores de memoria integrados y habilita una arquitectura de acceso a memoria no uniforme (NUMA).

Cada QPI comprende dos enlaces de datos punto a punto de 20 carriles, uno en cada dirección ( dúplex completo ), con un par de relojes separado en cada dirección, para un total de 42 señales. Cada señal es un par diferencial , por lo que el número total de pines es 84. Los 20 carriles de datos se dividen en cuatro "cuadrantes" de 5 carriles cada uno. La unidad básica de transferencia es el flit de 80 bits , que tiene 8 bits para la detección de errores, 8 bits para el "encabezado de la capa de enlace" y 64 bits para datos. Un flit de 80 bits se transfiere en dos ciclos de reloj (cuatro transferencias de 20 bits, dos por tic de reloj). Los anchos de banda de QPI se anuncian calculando la transferencia de 64 bits (8 bytes) de datos cada dos ciclos de reloj en cada dirección. [8]

Aunque las implementaciones iniciales utilizan enlaces de cuatro cuadrantes individuales, la especificación QPI permite otras implementaciones. Cada cuadrante se puede utilizar de forma independiente. En servidores de alta fiabilidad, un enlace QPI puede funcionar en un modo degradado. Si una o más de las 20+1 señales fallan, la interfaz funcionará utilizando 10+1 o incluso 5+1 señales restantes, incluso reasignando el reloj a una señal de datos si el reloj falla. [8] La implementación inicial de Nehalem utilizó una interfaz completa de cuatro cuadrantes para alcanzar 25,6 GB/s (6,4 GT/s × 1 byte × 4), lo que proporciona exactamente el doble del ancho de banda teórico del FSB de 1600 MHz de Intel utilizado en el chipset X48.

Aunque algunos procesadores Core i7 de alta gama exponen QPI, otros procesadores de escritorio y móviles Nehalem "convencionales" destinados a placas de un solo socket (por ejemplo, LGA 1156 Core i3, Core i5 y otros procesadores Core i7 de las familias Lynnfield / Clarksfield y sucesores) no exponen QPI externamente, porque estos procesadores no están destinados a participar en sistemas de múltiples sockets.

Sin embargo, QPI se utiliza internamente en estos chips para comunicarse con el " uncore ", que es parte del chip que contiene controladores de memoria, PCI Express del lado de la CPU y GPU, si está presente; el uncore puede o no estar en el mismo chip que el núcleo de la CPU, por ejemplo, está en un chip separado en Clarkdale / Arrandale basado en Westmere . [13] [14] [15] [16] : 3

En los chips de un solo socket posteriores a 2009, empezando por Lynnfield, Clarksfield, Clarkdale y Arrandale, las funciones tradicionales de puente norte están integradas en estos procesadores, que por lo tanto se comunican externamente a través de las interfaces DMI y PCI Express, más lentas.

Por lo tanto, no es necesario incurrir en el gasto de exponer la interfaz de bus frontal (anterior) a través del zócalo del procesador. [17]

Aunque el enlace QPI entre núcleo y núcleo no está presente en los procesadores Sandy Bridge de escritorio y móviles (como sí lo estaba en Clarkdale, por ejemplo), la interconexión de anillo interna entre los núcleos en el chip también se basa en los principios detrás de QPI, al menos en lo que respecta a la coherencia de caché . [16] : 10

Especificaciones de frecuencia

Al ser un circuito síncrono , el QPI opera a una frecuencia de reloj de 2,4 GHz, 2,93 GHz, 3,2 GHz, 3,6 GHz, 4,0 GHz o 4,8 GHz (las frecuencias de 3,6 GHz y 4,0 GHz se introdujeron con la plataforma Sandy Bridge-E/EP y las de 4,8 GHz con la plataforma Haswell-E/EP). La frecuencia de reloj de un enlace en particular depende de las capacidades de los componentes en cada extremo del enlace y de las características de la señal de la ruta de la señal en la placa de circuito impreso. Los procesadores Core i7 9xx no extremos están restringidos a una frecuencia de 2,4 GHz en los relojes de referencia de fábrica.

Las transferencias de bits ocurren tanto en los flancos ascendentes como descendentes del reloj, por lo que la tasa de transferencia es el doble de la frecuencia del reloj.

Intel describe el rendimiento de datos (en GB/s) contando solo la carga útil de datos de 64 bits en cada flit de 80 bits. Sin embargo, Intel duplica el resultado porque el par de enlaces de envío y recepción unidireccionales pueden estar activos simultáneamente. Por lo tanto, Intel describe un par de enlaces QPI de 20 carriles (envío y recepción) con una frecuencia de reloj de 3,2 GHz como si tuviera una velocidad de datos de 25,6 GB/s. Una frecuencia de reloj de 2,4 GHz produce una velocidad de datos de 19,2 GB/s. De manera más general, según esta definición, un QPI de 20 carriles y dos enlaces transfiere ocho bytes por ciclo de reloj, cuatro en cada dirección.

La tasa se calcula de la siguiente manera:

- 3,2 GHz

- × 2 bits/Hz (doble velocidad de datos)

- × 16(20) (bits de datos/ancho de enlace QPI)

- × 2 (envío y recepción unidireccionales que funcionan simultáneamente)

- ÷ 8 (bits/byte)

- = 25,6 GB/s

Capas de protocolo

QPI se especifica como una arquitectura de cinco capas , con capas físicas, de enlace, de enrutamiento, de transporte y de protocolo separadas. [1] En dispositivos destinados solo para uso de QPI punto a punto sin reenvío, como los procesadores Core i7-9xx y Xeon DP, la capa de transporte no está presente y la capa de enrutamiento es mínima.

- Capa física

- La capa física comprende el cableado real y los transmisores y receptores diferenciales, además de la lógica de nivel más bajo que transmite y recibe la unidad de la capa física. La unidad de la capa física es el "phit" de 20 bits. La capa física transmite un "phit" de 20 bits utilizando un único flanco de reloj en 20 carriles cuando los 20 carriles están disponibles, o en 10 o 5 carriles cuando el QPI se reconfigura debido a una falla. Tenga en cuenta que, además de las señales de datos, se envía una señal de reloj desde el transmisor al receptor (lo que simplifica la recuperación del reloj a expensas de pines adicionales).

- Capa de enlace

- La capa de enlace es responsable de enviar y recibir mensajes de 80 bits. Cada mensaje se envía a la capa física como cuatro mensajes de 20 bits. Cada mensaje contiene un CRC de 8 bits generado por el transmisor de la capa de enlace y una carga útil de 72 bits. Si el receptor de la capa de enlace detecta un error de CRC, el receptor notifica al transmisor a través de un mensaje en el enlace de retorno del par y el transmisor reenvía el mensaje. La capa de enlace implementa el control de flujo utilizando un esquema de crédito/débito para evitar que el búfer del receptor se desborde. La capa de enlace admite seis clases diferentes de mensajes para permitir que las capas superiores distingan los mensajes de datos de los mensajes que no son de datos, principalmente para el mantenimiento de la coherencia de la memoria caché. En implementaciones complejas de la arquitectura QuickPath, la capa de enlace se puede configurar para mantener flujos separados y control de flujo para las diferentes clases. No está claro si esto es necesario o se implementa para implementaciones de un solo procesador y de procesador dual.

- Capa de enrutamiento

- La capa de enrutamiento envía una unidad de 72 bits que consta de un encabezado de 8 bits y una carga útil de 64 bits. El encabezado contiene el destino y el tipo de mensaje. Cuando la capa de enrutamiento recibe una unidad, examina sus tablas de enrutamiento para determinar si la unidad ha llegado a su destino. Si es así, se envía a la capa inmediatamente superior. Si no, se envía en el QPI saliente correcto. En un dispositivo con un solo QPI, la capa de enrutamiento es mínima. Para implementaciones más complejas, las tablas de enrutamiento de la capa de enrutamiento son más complejas y se modifican dinámicamente para evitar enlaces QPI fallidos.

- Capa de transporte

- La capa de transporte no es necesaria y no está presente en dispositivos que están destinados únicamente a conexiones punto a punto. Esto incluye el Core i7. La capa de transporte envía y recibe datos a través de la red QPI desde sus pares en otros dispositivos que pueden no estar conectados directamente (es decir, los datos pueden haberse enrutado a través de un dispositivo intermedio). La capa de transporte verifica que los datos estén completos y, si no lo están, solicita la retransmisión de su par.

- Capa de protocolo

- La capa de protocolo envía y recibe paquetes en nombre del dispositivo. Un paquete típico es una fila de la memoria caché. La capa de protocolo también participa en el mantenimiento de la coherencia de la memoria caché mediante el envío y la recepción de mensajes relevantes.

Véase también

- Bus de interfaz elástica

- Autobús de la parte delantera

- Hipertransporte

- Lista de anchos de banda de dispositivos

- PCI Express

- RapidIO

Referencias

- ^ ab "Introducción a la interconexión Intel QuickPath" (PDF) . Intel Corporation. 30 de enero de 2009 . Consultado el 14 de junio de 2011 .

- ^ Informe de DailyTech Archivado el 17 de octubre de 2013 en Wayback Machine , consultado el 21 de agosto de 2007

- ^ Eva Glass (16 de mayo de 2007). «Se revela el nombre de Intel CSI: Slow, slow, quick quick slow» (Lento, lento, rápido, rápido, lento). The Inquirer . Archivado desde el original el 10 de junio de 2012. Consultado el 13 de septiembre de 2013 .

{{cite news}}: CS1 maint: URL no apta ( enlace ) - ^ David Kanter (20 de julio de 2011). "La evolución del camino rápido de Intel". Realworldtech.com . Consultado el 21 de enero de 2014 .

- ^ SoftPedia: Intel planea reemplazar Xeon con su nueva superplataforma “Purley” basada en Skylake

- ^ Gabriel Torres (25 de agosto de 2008). "Todo lo que necesita saber sobre QuickPath Interconnect (QPI)". Secretos de hardware . Consultado el 23 de enero de 2017 .

- ↑ Charlie Demerjian (13 de diciembre de 2005). «Intel Intel se pone nerviosa por Tanglewood». The Inquirer . Archivado desde el original el 3 de septiembre de 2010. Consultado el 13 de septiembre de 2013 .

{{cite news}}: CS1 maint: URL no apta ( enlace ) - ^ abc David Kanter (28 de agosto de 2007). «The Common System Interface: Intel's Future Interconnect». Real World Tech . Consultado el 14 de agosto de 2014 .

- ^ Eva Glass (12 de diciembre de 2004). «El Whitefield de Intel adopta la forma de un IA-32 de cuatro núcleos». The Inquirer . Archivado desde el original el 24 de mayo de 2009. Consultado el 13 de septiembre de 2013 .

{{cite news}}: CS1 maint: URL no apta ( enlace ) - ^ David Kanter (5 de mayo de 2006). «Se confirma que el procesador Tukwila de Intel tendrá cuatro núcleos». Real World Tech . Archivado desde el original el 10 de mayo de 2012. Consultado el 13 de septiembre de 2013 .

- ^ "Descripción técnica de la familia de procesadores escalables Intel® Xeon®".

- ^ "Intel demuestra el primer chip de 32 nm de la industria y la arquitectura de microprocesador Nehalem de próxima generación". Archivado desde el original el 2008-01-02 . Consultado el 2007-12-31 .

- ^ Chris Angelini (7 de septiembre de 2009). "QPI, memoria integrada, PCI Express y LGA 1156: Intel Core i5 y Core i7: la obra maestra de Intel". Tomshardware.com . Consultado el 21 de enero de 2014 .

- ^ Publicado el 25 de enero de 2010 por Richard Swinburne (25 de enero de 2010). "Característica: rendimiento de gráficos Intel GMA HD". bit-tech.net . Consultado el 21 de enero de 2014 .

{{cite web}}: CS1 maint: nombres numéricos: lista de autores ( enlace ) - ^ "Se realizó un análisis comparativo del chip de CPU y GPU Intel Clarkdale de 32 nm (nuevamente) - CPU - Característica". HEXUS.net. 25 de septiembre de 2009. Consultado el 21 de enero de 2014 .

- ^ por Oded Lempel (28 de julio de 2013). «Familia de procesadores Intel Core de segunda generación: Intel Core i7, i5 e i3» (PDF) . hotchips.org . Archivado desde el original (PDF) el 29 de julio de 2020. Consultado el 21 de enero de 2014 .

- ^ Lily Looi, Stephan Jourdan, Transición de las microarquitecturas de próxima generación de Intel® (Nehalem y Westmere) a la corriente principal Archivado el 2 de agosto de 2020 en Wayback Machine , Hot Chips 21, 24 de agosto de 2009

Enlaces externos

- Introducción a la interconexión Intel QuickPath

- Descripción general de la interconexión Intel QuickPath Archivado el 2 de febrero de 2014 en Wayback Machine (PDF)

- Lo que necesita saber sobre la CPU Nehalem de Intel, Ars Technica , 9 de abril de 2008, por Jon Stokes

- Primer vistazo a la microarquitectura de Nehalem: bus QPI Archivado el 14 de mayo de 2016 en Wayback Machine , 2 de noviembre de 2008, por Ilya Gavrichenkov

- La interfaz de sistema común: la interconexión del futuro de Intel, 28 de agosto de 2007, por David Kanter