Intel 8087

| |

| información general | |

|---|---|

| Lanzado | 1980 ( 1980 ) |

| Interrumpido | 28 de septiembre de 2007 [1] ( 28-09-2007 ) |

| Comercializado por | Intel , IBM [2] |

| Diseñado por | Intel |

| Fabricantes comunes | |

| Actuación | |

| Frecuencia máxima de reloj de la CPU | De 4 MHz a 10 MHz |

| Arquitectura y clasificación | |

| Nodo tecnológico | 4,5->3 μm |

| Conjunto de instrucciones | x87 ( extensión del coprocesador x86-16 ) |

| Especificaciones físicas | |

| Transistores |

|

| Paquete |

|

| Historia | |

| Predecesor | 8231/8232 |

| Sucesor | 80287 |

El Intel 8087 , anunciado en 1980, fue el primer coprocesador de punto flotante para la línea de microprocesadores 8086. [5] [6] [7] El propósito del chip era acelerar las operaciones aritméticas de punto flotante , como la suma , la resta , la multiplicación , la división y la raíz cuadrada . También calcula funciones trascendentales como cálculos exponenciales , logarítmicos o trigonométricos . Las mejoras de rendimiento fueron de aproximadamente el 20% a más del 500%, dependiendo de la aplicación específica. El 8087 podía realizar alrededor de 50.000 FLOPS [6] utilizando alrededor de 2,4 vatios. [7]

El 8087 era un circuito integrado avanzado que superaba los límites de la tecnología de fabricación de la época. [ cita requerida ] Las operaciones básicas del 8087, como la suma y la resta, pueden tardar más de 100 ciclos de máquina en ejecutarse y algunas instrucciones superan los 1000 ciclos. [8] El chip carece de un multiplicador de hardware e implementa cálculos utilizando el algoritmo CORDIC . [9]

Las ventas del 8087 recibieron un impulso significativo cuando se incluyó un zócalo de coprocesador en la placa base del IBM PC de 1981. El desarrollo del 8087 condujo al estándar IEEE 754-1985 para aritmética de punto flotante. Las versiones de velocidad disponibles fueron 4,77 (5), 8 y 10 MHz. [10] Hubo coprocesadores x87 posteriores para los procesadores 80186 , 80286 , 80386 y 80386SX . A partir del 80486DX , los procesadores Intel x86 presentaban coprocesadores de punto flotante integrados; las funciones de punto flotante se integraban con el procesador. Los procesadores Intel 486SX tienen una unidad de punto flotante deshabilitada o ausente, pero permiten un 80487 separado.

El Intel 80186 y sus productos asociados se discontinuaron el 30 de marzo de 2007 para pedidos y el 28 de septiembre de 2007 para envíos. [11]

Variantes

| Número de modelo [12] | Frecuencia | Nombre del modelo | (USD) [lista 1] |

|---|---|---|---|

| 8087 | 5 MHz | CAJA8087 | $142 |

| 8087-2 | 8 MHz | CAJA8087-2 | $205 |

| 8087-1 | 10 MHz | CAJA8087-1 | $270 |

- ^ Precio unitario sugerido

Diseño y desarrollo

Intel había fabricado anteriormente la unidad de procesamiento aritmético 8231 y el procesador de punto flotante 8232. Estos fueron diseñados para su uso con procesadores 8080 o similares y utilizaban un bus de datos de 8 bits. Se interconectaban a un sistema host a través de E/S programadas o un controlador DMA . [13]

El 8087 fue concebido inicialmente por Bill Pohlman, el director de ingeniería de Intel que supervisó el desarrollo del chip 8086. Bill tomó medidas para asegurarse de que el chip 8086 pudiera soportar un chip matemático que aún no se había desarrollado.

En 1977, Pohlman recibió el visto bueno para diseñar el chip matemático 8087. Bruce Ravenel fue designado como arquitecto y John Palmer fue contratado como coarquitecto y matemático del proyecto. Los dos idearon un diseño revolucionario con 64 bits de mantisa y 16 bits de exponente para el número real de formato más largo, con una CPU de arquitectura de pila y ocho registros de pila de 80 bits, con un conjunto de instrucciones computacionalmente rico. El diseño resolvió algunos problemas conocidos destacados en computación numérica y software numérico: se eliminaron los problemas de error de redondeo para operandos de 64 bits y se resolvieron las conversiones de modo numérico para todos los números de 64 bits. Palmer atribuyó los escritos de William Kahan sobre el punto flotante como una influencia significativa en su diseño. [14]

El diseño del 8087 tuvo inicialmente una recepción fría en Santa Clara debido a su diseño agresivo. Finalmente, el diseño fue asignado a Intel Israel, y Rafi Nave fue designado para liderar la implementación del chip. Palmer, Ravenel y Nave obtuvieron patentes por el diseño. [15] Robert Koehler y John Bayliss también obtuvieron una patente por la técnica en la que algunas instrucciones con un patrón de bits particular se descargaban al coprocesador. [16]

El 8087 tenía 65.000 transistores y se fabricó como un circuito HMOS de carga de agotamiento de 4,5 μm (luego reducido a 3 μm) . Funcionó en tándem con el 8086 o el 8088 e introdujo alrededor de 60 nuevas instrucciones . La mayoría de las mnemotecnias de ensamblaje del 8087 comienzan con F, como FADD, FMUL, FCOM, etc., lo que las hace fácilmente distinguibles de las instrucciones del 8086. Las codificaciones binarias para todas las instrucciones del 8087 comienzan con el patrón de bits 11011, decimal 27, el mismo que el carácter ASCII ESC, aunque en los bits de orden superior de un byte; los prefijos de instrucciones similares también se denominan a veces " códigos de escape ". La mnemotecnia de instrucción asignada por Intel para estas instrucciones de coprocesador es "ESC". El 8087 era caro y difícil de fabricar con bajos rendimientos. También se calentaba bastante, lo que obligó a Intel a utilizar un paquete de cerámica más caro para mejorar la disipación térmica.

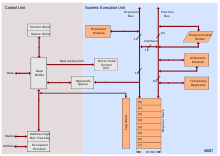

Cuando la CPU 8086 o 8088 ejecutaba la instrucción ESC, si el segundo byte (el byte ModR/M) especificaba un operando de memoria, la CPU ejecutaba un ciclo de bus para leer una palabra de la ubicación de memoria especificada en la instrucción (usando cualquier modo de direccionamiento 8086), pero no almacenaba el operando leído en ningún registro de la CPU ni realizaba ninguna operación en él; el 8087 observaba el bus y decodificaba el flujo de instrucciones en sincronía con el 8086, reconociendo las instrucciones del coprocesador destinadas a sí mismo. Para una instrucción 8087 con un operando de memoria, si la instrucción solicitaba que se leyera el operando, el 8087 tomaba la palabra de datos leída por la CPU principal del bus de datos. Si el operando a leer era más largo que una palabra, el 8087 también copiaba la dirección del bus de direcciones; Luego, después de completar el ciclo de lectura de datos impulsado por la CPU, el 8087 usaría inmediatamente DMA para tomar el control del bus y transferir los bytes adicionales del operando mismo. Si una instrucción del 8087 con un operando de memoria requería que se escribiera ese operando, el 8087 ignoraría la palabra leída en el bus de datos y simplemente copiaría la dirección, luego solicitaría DMA y escribiría el operando completo, de la misma manera que leería el final de un operando extendido. De esta manera, la CPU principal mantenía el control general del bus y la temporización del bus, mientras que el 8087 manejaba todos los demás aspectos de la ejecución de las instrucciones del coprocesador, excepto por breves períodos de DMA cuando el 8087 tomaría el control del bus para leer o escribir operandos hacia/desde sus propios registros internos. Como consecuencia de este diseño, el 8087 solo podía operar en operandos tomados de la memoria o de sus propios registros, y cualquier intercambio de datos entre el 8087 y el 8086 o el 8088 era solo a través de la RAM.

El programa principal de la CPU continuaba ejecutándose mientras el 8087 ejecutaba una instrucción; desde la perspectiva de la CPU principal 8086 o 8088, una instrucción del coprocesador tomaba solo el tiempo que el procesamiento del código de operación y cualquier ciclo de operando de memoria (2 ciclos de reloj para ningún operando, 8 ciclos de reloj más el tiempo de cálculo de EA [5 a 12 ciclos de reloj] para un operando de memoria [más 4 ciclos de reloj más en un 8088], para transferir el segundo byte de la palabra del operando), después de lo cual la CPU comenzaría a ejecutar la siguiente instrucción del programa. Por lo tanto, un sistema con un 8087 era capaz de un verdadero procesamiento paralelo, realizando una operación en la ALU de enteros de la CPU principal mientras al mismo tiempo realizaba una operación de punto flotante en el coprocesador 8087. Dado que el 8086 o el 8088 controlaban exclusivamente el flujo y la temporización de las instrucciones y no tenían acceso directo al estado interno del 8087, y debido a que el 8087 sólo podía ejecutar una instrucción a la vez, los programas para el sistema combinado 8086/8087 o 8088/8087 tenían que garantizar que el 8087 tuviera tiempo de completar la última instrucción que se le había emitido antes de que se le emitiera otra. La instrucción WAIT (de la CPU principal) se proporcionó para este propósito, y la mayoría de los ensambladores implícitamente afirmaban una instrucción WAIT antes de cada instancia de la mayoría de las instrucciones del coprocesador de punto flotante. (No es necesario utilizar una instrucción WAIT antes de una operación 8087 si el programa utiliza otros medios para asegurar que transcurra suficiente tiempo entre la emisión de instrucciones 8087 sensibles al tiempo de modo que el 8087 nunca pueda recibir dicha instrucción antes de completar la anterior. Tampoco es necesario, si se utiliza una instrucción WAIT, que preceda inmediatamente a la siguiente instrucción 8087). La instrucción WAIT esperaba a que se activara el pin de entrada −TEST del 8086/8088 (bajo), y este pin se conectaba al pin BUSY del 8087 en todos los sistemas que tenían un 8087 (de modo que TEST se activaba cuando se desactivaba BUSY).

Debido a que las colas de precarga de instrucciones del 8086 y 8088 hacen que el momento en que se ejecuta una instrucción no siempre sea el mismo que el momento en que se obtiene, un coprocesador como el 8087 no puede determinar cuándo una instrucción para sí mismo es la siguiente instrucción que se ejecutará simplemente observando el bus de la CPU. El 8086 y el 8088 tienen dos señales de estado de cola conectadas al coprocesador para permitirle sincronizarse con el tiempo interno de ejecución de instrucciones de la CPU desde su cola de precarga. El 8087 mantiene su propia cola de precarga idéntica, desde la cual lee los códigos de operación del coprocesador que realmente ejecuta. Debido a que las colas de precarga del 8086 y 8088 tienen diferentes tamaños y diferentes algoritmos de administración, el 8087 determina a qué tipo de CPU está conectado observando una determinada línea de bus de CPU cuando se reinicia el sistema, y el 8087 ajusta su cola de instrucciones interna en consecuencia. La duplicación redundante del hardware de la cola de precarga en la CPU y el coprocesador es ineficiente en términos de consumo de energía y área total de chip, pero permitió que la interfaz del coprocesador utilizara muy pocos pines de CI dedicados, lo cual era importante. En el momento en que se introdujo el 8086, que definió la interfaz del coprocesador, los paquetes de CI con más de 40 pines eran raros, caros y sufrían problemas como una capacitancia excesiva de los cables, un factor limitante importante para las velocidades de señalización.

Los códigos de operación del coprocesador están codificados en 6 bits en 2 bytes, comenzando con la secuencia de escape:

┌───────────┬───────────┐ │ 1101 1xxx │ mmxx xrrr │ └───────────┴───────────┘

Los primeros tres bits "x" son los primeros tres bits del código de operación de punto flotante. Luego vienen dos bits "m", luego la última mitad de los tres bits del código de operación de punto flotante, seguidos de tres bits "r". Los bits "m" y "r" especifican la información del modo de direccionamiento. [17]

Los programas de aplicación debían escribirse para hacer uso de las instrucciones especiales de punto flotante. En tiempo de ejecución, el software podía detectar el coprocesador y utilizarlo para operaciones de punto flotante. Cuando se detectaba su ausencia, debían calcularse funciones de punto flotante similares en el software, o bien se podía emular todo el coprocesador en el software para lograr una compatibilidad numérica más precisa. [18]

Registros

La familia x87 no utiliza un conjunto de registros directamente direccionables como los registros principales de los procesadores x86; en su lugar, los registros x87 forman una estructura de pila profunda de ocho niveles [19] que va desde st0 a st7, donde st0 es la parte superior. Las instrucciones x87 operan insertando, calculando y extrayendo valores en esta pila. Sin embargo, las operaciones diádicas como FADD, FMUL, FCMP, etc. pueden utilizar implícitamente los st0 y st1 superiores o pueden utilizar st0 junto con un operando o registro de memoria explícito ; el registro st0 puede utilizarse así como un acumulador (es decir, como un destino combinado y un operando izquierdo) y también puede intercambiarse con cualquiera de los ocho registros de la pila utilizando una instrucción llamada FXCH st X (códigos D9C8–D9CF h ). Esto hace que la pila x87 se pueda utilizar como siete registros libremente direccionables más un acumulador. Esto es especialmente aplicable en procesadores x86 superescalares ( Pentium de 1993 y posteriores), donde estas instrucciones de intercambio están optimizadas hasta una penalización de reloj cero.

Estándar de punto flotante IEEE

Cuando Intel diseñó el 8087, su objetivo era crear un formato de punto flotante estándar para futuros diseños. Un aspecto importante del 8087 desde una perspectiva histórica fue que se convirtió en la base del estándar de punto flotante IEEE 754. El 8087 no implementó el eventual estándar IEEE 754 en todos sus detalles, ya que el estándar no se terminó hasta 1985, pero el 80387 sí lo hizo. El 8087 proporcionó dos tipos de datos de punto flotante básicos de 32/64 bits y un formato temporal interno extendido adicional de 80 bits (que también podía almacenarse en la memoria) para mejorar la precisión en cálculos grandes y complejos. Aparte de esto, el 8087 ofrecía un formato BCD ( decimal codificado en binario ) empaquetado de 80 bits/18 dígitos y tipos de datos enteros de 16, 32 y 64 bits. [19]

| 8087 tipos de datos | |||||||||||||||||

| 7 9 | ... | 7 1 | ... | 6 7 | ... | 6 3 | ... | 5 0 | ... | 3 1 | ... | 2 2 | ... | 1 5 | ... | 0 0 | (posición de bit) |

| ± | Exponente | Fracción | Precisión extendida de 80 bits real | ||||||||||||||

| ± | Exponente | Fracción | 64 bits de doble precisión real | ||||||||||||||

| ± | Exponente | Fracción | Real de precisión simple de 32 bits | ||||||||||||||

| ± | Número entero BCD | Entero decimal de 18 dígitos | |||||||||||||||

| ± | Entero | Entero binario de 64 bits | |||||||||||||||

| ± | Entero | Entero binario de 32 bits | |||||||||||||||

| ± | Entero | Entero binario de 16 bits | |||||||||||||||

Infinidad

El 8087 maneja valores infinitos ya sea por cierre afín o cierre proyectivo (seleccionado por el registro de estado). Con el cierre afín, los infinitos positivos y negativos se tratan como valores diferentes. Con el cierre proyectivo, el infinito se trata como una representación sin signo para números muy pequeños o muy grandes. [20] Estos dos métodos de manejo del infinito se incorporaron en la versión borrador del estándar de punto flotante IEEE 754. Sin embargo, el cierre proyectivo ( sistema de números reales extendido proyectivamente ) se eliminó de la edición formal posterior de IEEE 754-1985. El 80287 mantuvo el cierre proyectivo como una opción, pero el 80387 y los procesadores de punto flotante posteriores (incluido el 80187) solo admitieron el cierre afín.

Interfaz del coprocesador

El 8087 se diferenciaba de los coprocesadores Intel posteriores en que estaba conectado directamente a los buses de dirección y datos. El 8087 buscaba instrucciones que comenzaban con la secuencia "11011" y actuaba en consecuencia, solicitando inmediatamente DMA a la CPU principal según fuera necesario para acceder a operandos de memoria de más de una palabra (16 bits), y luego devolviendo inmediatamente el control del bus a la CPU principal. El coprocesador no detenía la ejecución del programa hasta que se completaba la instrucción del coprocesador, y el programa tenía que sincronizar explícitamente los dos procesadores, como se explicó anteriormente (en la sección "Diseño y desarrollo"). Existía un problema de posible bloqueo si la instrucción del coprocesador no lograba decodificarse a una que el coprocesador entendiera. Los coprocesadores posteriores de Intel no se conectaban a los buses de la misma manera, sino que recibían instrucciones a través de los puertos de E/S del procesador principal. Esto generaba una penalización en el tiempo de ejecución, pero se evitaba el problema de posible bloqueo porque el procesador principal ignoraba la instrucción si el coprocesador se negaba a aceptarla. El 8087 pudo detectar si estaba conectado a un 8088 o un 8086 al monitorear el bus de datos durante el ciclo de reinicio.

En teoría, el 8087 era capaz de trabajar simultáneamente mientras el 8086/8 procesaba instrucciones adicionales. En la práctica, existía la posibilidad de que el programa fallara si el coprocesador emitía una nueva instrucción antes de que se completara la última. El ensamblador insertaba automáticamente una instrucción FWAIT después de cada código de operación del coprocesador, lo que obligaba al 8086/8 a detener la ejecución hasta que el 8087 señalara que había terminado. [21] Esta limitación se eliminó de los diseños posteriores.

Sucesores

Así como los procesadores 8088 y 8086 fueron reemplazados por partes posteriores, también lo fue el 8087. Otros coprocesadores de Intel fueron el 80287 (en realidad, 80C287 , ya que Intel pasó a un proceso CMOS en ese momento), el 80387 y el 80187. A partir del 80486, los procesadores Intel posteriores no utilizaron un coprocesador de punto flotante separado; prácticamente todos lo incluyeron en la matriz del procesador principal, con la significativa excepción del 80486SX, que era un 80486DX modificado con la FPU deshabilitada. El 80487 era de hecho un chip 80486DX completo con un pin adicional. Cuando se instalaba, deshabilitaba la CPU 80486SX. Los procesadores 80486DX , Pentium y posteriores incluyen funcionalidad de punto flotante en el núcleo de la CPU.

Referencias

- ^ "Notificación de cambio de producto" (PDF) . 2 de mayo de 2006. Archivado desde el original (PDF) el 9 de octubre de 2006.

- ^ Shvets, Gennadiy (8 de octubre de 2011). «Unidad de punto flotante IBM 8087». CPU World . Consultado el 1 de diciembre de 2011 .

- ^ Shvets, Gennadiy (8 de octubre de 2011). «Unidad de punto flotante AMD 8087». CPU World . Consultado el 1 de diciembre de 2011 .

- ^ Shvets, Gennadiy (8 de octubre de 2011). «Unidad de punto flotante Cyrix 8087». CPU World . Consultado el 1 de diciembre de 2011 .

- ^ Palmer, John F. (1980). "El procesador de datos numéricos INTEL® 8087" (PDF) . AFIPS '80, Actas de la Conferencia Nacional de Computación, 19-22 de mayo de 1980. Anaheim, California: ACM. págs. 887-893. doi :10.1145/1500518.1500674.

- ^ ab "8087". Información sobre el punto del coprocesador . 2007. Archivado desde el original el 30 de septiembre de 2011. Consultado el 1 de diciembre de 2011 .

- ^ ab "Intel FPU". cpu-collection.de . 2011 . Consultado el 1 de diciembre de 2011 .

- ^ "Hoja de datos del Intel 8087".

- ^ Shirriff, Ken (mayo de 2020). "Extracción de constantes de ROM de la matriz del coprocesador matemático 8087". righto.com . Autopublicado por Ken Shirriff . Consultado el 3 de septiembre de 2020 .

La ROM contiene 16 valores de arcotangente, los arctangentes de 2

−n

. También contiene 14 valores de logaritmo, los logaritmos en base 2 de (1+2

−n

). Estos pueden parecer valores inusuales, pero se utilizan en un algoritmo eficiente llamado CORDIC, que se inventó en 1958.

- ^ Yoshida, Stacy, "Coprocesadores matemáticos: cómo mantener su computadora en óptimas condiciones", Intel Corporation, Microcomputer Solutions, septiembre/octubre de 1990, página 16

- ^ "Notificación de cambio de producto" (PDF) . 2 de mayo de 2006. Archivado desde el original (PDF) el 9 de octubre de 2006.

- ^ Intel Corporation, "Lista de precios de productos Intel para el mejoramiento de computadoras personales vigente a partir del 1 de noviembre de 1989", Personal Computer Enhancement Operation, orden n.° 245.2, 10-89/75K/AL/GO, octubre de 1989

- ^ Catálogo de datos de componentes Intel 1980 , número de catálogo Intel C-864/280/150K/CP, páginas 8-21, 8-28.

- ^ Sánchez y Cantón 2007, p. 96.

- ^ US 4484259, "Bus de fracciones para uso en un procesador de datos numéricos"

- ^ US 4270167, "Circuito de sincronización de unidad central de procesamiento dúplex"

- ^ Lemone, Karen A. (1985). Lenguaje ensamblador y programación de sistemas para IBM PC y compatibles. Little Brown. pág. 302. ISBN 978-0-316-52069-0.

- ^ Mueller, Scott (1992). Actualización y reparación de PC (2.ª ed.). Que. pp. 395–403. ISBN 0-88022-856-3.

- ^ ab Shvets, Gennadiy (8 de octubre de 2011). «Familia Intel 8087». CPU World . Consultado el 1 de diciembre de 2011 .

- ^ Sánchez y Cantón 2007, p. 110.

- ^ Lemone 1985, pág. 300

Bibliografía

- Sánchez, Julio; Cantón, María P. (2007). Soluciones de software para ingenieros y científicos . CRC Press. ISBN 978-1-4200-4302-0.

Enlaces externos

- Coprocesadores matemáticos Intel 80x87 en cpu-collection.de

- Coprocessor.info: información histórica y fotografías del coprocesador matemático 8087

- Hoja de datos del coprocesador matemático Intel 8087

- Shirriff, Ken (mayo de 2020). "Análisis de matriz del desplazador de bits rápido del coprocesador matemático 8087".