Paquete doble en línea

En microelectrónica , un encapsulado dual en línea ( DIP o DIL ) [1] es un encapsulado de componentes electrónicos con una carcasa rectangular y dos filas paralelas de pines de conexión eléctrica. El encapsulado puede montarse mediante orificios pasantes en una placa de circuito impreso (PCB) o insertarse en un zócalo. El formato dual en línea fue inventado por Don Forbes, Rex Rice y Bryant Rogers en Fairchild R&D en 1964, [2] cuando el número restringido de conductores disponibles en encapsulados circulares de estilo transistor se convirtió en una limitación en el uso de circuitos integrados . [3] Los circuitos cada vez más complejos requerían más conductores de señal y de fuente de alimentación (como se observa en la regla de Rent ); con el tiempo, los microprocesadores y dispositivos complejos similares requirieron más conductores de los que se podían colocar en un encapsulado DIP, lo que llevó al desarrollo de portadores de chip de mayor densidad . Además, los encapsulados cuadrados y rectangulares facilitaron el enrutamiento de trazas de circuitos impresos debajo de los encapsulados.

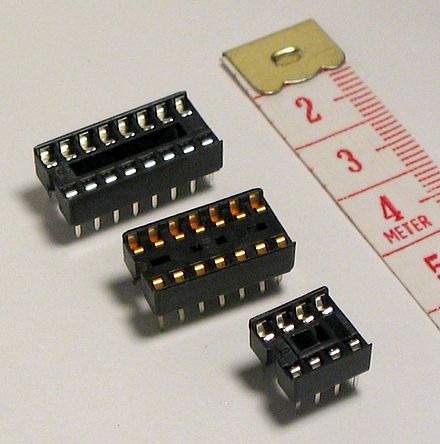

Un DIP se suele denominar DIP n , donde n es el número total de pines y, a veces, se le añade el ancho del encapsulado fila a fila "N" para estrecho (0,3") o "W" para ancho (0,6"). Por ejemplo, un encapsulado de microcircuito con dos filas de siete conductores verticales sería un DIP14 o DIP14N. La fotografía de la parte superior derecha muestra tres circuitos integrados DIP14. Los encapsulados comunes tienen tan solo tres y hasta 64 conductores. Muchos tipos de circuitos integrados analógicos y digitales están disponibles en encapsulados DIP, al igual que matrices de transistores, interruptores, diodos emisores de luz y resistencias. Los conectores DIP para cables planos se pueden utilizar con zócalos de circuitos integrados estándar.

Los encapsulados DIP suelen estar hechos de un plástico epoxi moldeado opaco prensado alrededor de un marco de conductores chapado en estaño, plata u oro que sostiene la matriz del dispositivo y proporciona pines de conexión. Algunos tipos de CI se fabrican en encapsulados DIP de cerámica, donde se requiere alta temperatura o alta confiabilidad, o donde el dispositivo tiene una ventana óptica hacia el interior del encapsulado. La mayoría de los encapsulados DIP se fijan a una PCB insertando los pines a través de orificios en la placa y soldándolos en su lugar. Cuando es necesario reemplazar las piezas, como en dispositivos de prueba o donde se deben quitar dispositivos programables para realizar cambios, se utiliza un zócalo DIP. Algunos zócalos incluyen un mecanismo de fuerza de inserción cero (ZIF).

Las variaciones del encapsulado DIP incluyen aquellos con una sola fila de pines, por ejemplo, una matriz de resistencias , posiblemente incluyendo una pestaña disipadora de calor en lugar de la segunda fila de pines, y tipos con cuatro filas de pines, dos filas, escalonadas, en cada lado del encapsulado. Los encapsulados DIP han sido reemplazados en su mayoría por tipos de encapsulados de montaje superficial, que evitan el gasto de perforar agujeros en una PCB y que permiten una mayor densidad de interconexiones.

Aplicaciones

Tipos de dispositivos

Los DIP se utilizan comúnmente para circuitos integrados (CI). Otros dispositivos en encapsulados DIP incluyen redes de resistencias, interruptores DIP , pantallas LED segmentadas y gráficas de barras, y relés electromecánicos .

Los conectores DIP para cables planos son comunes en computadoras y otros equipos electrónicos.

Dallas Semiconductor fabricó módulos de reloj en tiempo real (RTC) DIP integrados que contenían un chip IC y una batería de litio no reemplazable de 10 años.

Los bloques de encabezado DIP a los que se podían soldar componentes discretos se utilizaron cuando era necesario quitar fácilmente grupos de componentes para realizar cambios de configuración, funciones opcionales o calibración.

Usos

El encapsulado dual-in-line original fue inventado por Bryant "Buck" Rogers en 1964 mientras trabajaba para Fairchild Semiconductor. Los primeros dispositivos tenían 14 pines y se parecían mucho a los actuales. [4] La forma rectangular permitió que los circuitos integrados se encapsularan de forma más densa que los encapsulados redondos anteriores. [5] El encapsulado era muy adecuado para equipos de ensamblaje automatizado; una PCB podía llenarse con decenas o cientos de circuitos integrados, luego todos los componentes de la placa de circuito podían soldarse a la vez en una máquina de soldadura por ola y pasarse a máquinas de prueba automatizadas, con muy poca mano de obra humana requerida. Los encapsulados DIP todavía eran grandes con respecto a los circuitos integrados que contenían. A fines del siglo XX, los encapsulados de montaje superficial permitieron una mayor reducción en el tamaño y el peso de los sistemas. Los chips DIP todavía son populares para la creación de prototipos de circuitos en una placa de pruebas debido a la facilidad con la que se pueden insertar y usar allí.

Los DIP fueron la corriente principal de la industria de la microelectrónica en las décadas de 1970 y 1980. Su uso ha disminuido en la primera década del siglo XXI debido a los nuevos paquetes de tecnología de montaje superficial (SMT) emergentes, como el portador de chip con conductores de plástico (PLCC) y el circuito integrado de contorno pequeño (SOIC), aunque los DIP continuaron utilizándose ampliamente durante la década de 1990 y todavía continúan utilizándose sustancialmente a finales del año 2011. Debido a que algunos chips modernos solo están disponibles en tipos de paquetes de montaje superficial, varias empresas venden varios adaptadores de prototipado para permitir que esos dispositivos de montaje superficial (SMD) se usen como dispositivos DIP con placas de pruebas de orificios pasantes y placas de prototipado soldadas (como stripboard y perfboard ). (SMT puede plantear un gran problema, al menos un inconveniente, para el prototipado en general; la mayoría de las características de SMT que son ventajas para la producción en masa son dificultades para el prototipado).

Para dispositivos programables como EPROM y GAL , los DIP siguieron siendo populares durante muchos años debido a su fácil manejo con circuitos de programación externos (es decir, los dispositivos DIP se podían conectar simplemente a un zócalo en el dispositivo de programación). Sin embargo, con la tecnología de programación en el sistema (ISP) ahora de última generación, esta ventaja de los DIP también está perdiendo importancia rápidamente.

Durante la década de 1990, se fabricaron dispositivos con menos de 20 derivaciones en formato DIP, además de los formatos más nuevos. Desde aproximadamente el año 2000, los dispositivos más nuevos no suelen estar disponibles en formato DIP.

Montaje

Los DIP se pueden montar mediante soldadura a través de orificios pasantes o en zócalos. Los zócalos permiten reemplazar fácilmente un dispositivo y eliminan el riesgo de daños por sobrecalentamiento durante la soldadura. Por lo general, los zócalos se usaban para circuitos integrados de gran valor o de gran tamaño, que cuestan mucho más que el zócalo. En los casos en que los dispositivos se insertan y extraen con frecuencia, como en equipos de prueba o programadores de EPROM, se usaba un zócalo de fuerza de inserción cero .

Los DIP también se utilizan con placas de pruebas, un sistema de montaje temporal para fines educativos, desarrollo de diseño o pruebas de dispositivos. Algunos aficionados, para construcciones únicas o prototipos permanentes, utilizan cableado punto a punto con DIP, y su apariencia cuando se invierte físicamente como parte de este método inspira el término informal "estilo insecto muerto" para el método.

- Zócalos DIP de 0,3" de ancho con contactos de doble barrido para circuitos integrados DIP de 16, 14 y 8 pines

- Zócalo DIP de 16 pines de 0,3" de ancho con contactos redondos mecanizados para circuito integrado DIP16

- Zócalo de fuerza de inserción cero (ZIF) para circuito integrado DIP28W de 0,6" de ancho, comúnmente utilizado en programadores de circuitos integrados EPROM

- Zócalo DIP de 0,3" de ancho para circuito integrado DIP28 angosto, también conocido como DIP28N, comúnmente utilizado en placas Arduino más antiguas

Construcción

El cuerpo (carcasa) de un DIP que contiene un chip IC suele estar fabricado con plástico moldeado o cerámica. La naturaleza hermética de una carcasa de cerámica es la preferida para dispositivos de fiabilidad extremadamente alta. Sin embargo, la gran mayoría de los DIP se fabrican mediante un proceso de moldeo termoendurecible en el que se calienta un compuesto de moldeo de epoxi y se transfiere bajo presión para encapsular el dispositivo. Los ciclos de curado típicos para las resinas son inferiores a 2 minutos y un solo ciclo puede producir cientos de dispositivos.

Los cables emergen de los lados más largos del paquete a lo largo de la costura, paralelos a los planos superior e inferior del paquete, y se doblan hacia abajo aproximadamente 90 grados (o ligeramente menos, dejándolos en un ángulo ligeramente hacia afuera desde la línea central del cuerpo del paquete). (El SOIC , el paquete SMT que más se parece a un DIP típico, parece esencialmente el mismo, a pesar de la escala de tamaño, excepto que después de doblarse hacia abajo, los cables se doblan hacia arriba nuevamente en un ángulo igual para volverse paralelos al plano inferior del paquete). En los paquetes cerámicos (CERDIP), se utiliza un epoxi o lechada para sellar herméticamente las dos mitades juntas, proporcionando un sello hermético al aire y la humedad para proteger el chip IC en el interior. Los paquetes DIP de plástico (PDIP) generalmente se sellan fusionando o cementando las mitades de plástico alrededor de los cables, pero no se logra un alto grado de hermeticidad porque el plástico en sí suele ser algo poroso a la humedad y el proceso no puede garantizar un buen sello microscópico entre los cables y el plástico en todos los puntos alrededor del perímetro. Sin embargo, los contaminantes generalmente se mantienen alejados lo suficientemente bien como para que el dispositivo pueda funcionar de manera confiable durante décadas con un cuidado razonable en un entorno controlado.

Dentro del encapsulado, la mitad inferior tiene los cables incrustados, y en el centro del encapsulado hay un espacio, cámara o vacío rectangular en el que se cementa el chip del CI. Los cables del encapsulado se extienden diagonalmente dentro del encapsulado desde sus posiciones de emergencia a lo largo de la periferia hasta puntos a lo largo de un perímetro rectangular que rodea el chip, estrechándose a medida que avanzan para convertirse en contactos finos en el chip. Cables de unión ultrafinos (apenas visibles para el ojo humano desnudo) están soldados entre estos contactos de la periferia del chip y las almohadillas de unión en el propio chip, conectando un cable a cada almohadilla de unión y haciendo la conexión final entre los microcircuitos y los cables DIP externos. Los cables de unión no suelen estar tensos, sino que se enrollan ligeramente hacia arriba para permitir la holgura para la expansión y contracción térmica de los materiales; si un solo cable de unión se rompe o se desprende, todo el CI puede quedar inutilizable. La parte superior del encapsulado cubre todo este delicado conjunto sin aplastar los cables de unión, protegiéndolo de la contaminación por materiales extraños.

Por lo general, se imprime un logotipo de la empresa, códigos alfanuméricos y, a veces, palabras en la parte superior del paquete para identificar su fabricante y tipo, cuándo se fabricó (generalmente como un año y un número de semana), a veces dónde se fabricó y otra información de propiedad (tal vez números de revisión, códigos de planta de fabricación o códigos de identificación de pasos).

La necesidad de disponer todos los cables en un patrón básicamente radial en un solo plano desde el perímetro de la matriz hasta dos filas en la periferia del encapsulado es la razón principal por la que los encapsulados DIP con mayor cantidad de cables deben tener un espaciado más amplio entre las filas de cables, y limita de manera efectiva la cantidad de cables que puede tener un encapsulado DIP práctico. Incluso para una matriz muy pequeña con muchos pads de unión (por ejemplo, un chip con 15 inversores, que requiere 32 cables), se requeriría un DIP más ancho para acomodar los cables radiantes internamente. Esta es una de las razones por las que se introdujeron los encapsulados de cuatro lados y múltiples filas, como los PGA (alrededor de principios de la década de 1980).

Un paquete DIP grande (como el DIP64 utilizado para la CPU Motorola 68000 ) tiene cables largos dentro del paquete entre los pines y la matriz, lo que hace que dicho paquete no sea adecuado para dispositivos de alta velocidad.

Otros tipos de dispositivos DIP se construyen de forma muy diferente. La mayoría de ellos tienen carcasas de plástico moldeado y cables rectos o cables que se extienden directamente desde la parte inferior del paquete. En algunos casos, en particular en el caso de las pantallas LED, la carcasa suele ser una caja de plástico hueca con la parte inferior/posterior abierta, rellena (alrededor de los componentes electrónicos que contiene) con un material epoxi translúcido duro del que emergen los cables. Otros, como los interruptores DIP, se componen de dos (o más) piezas de carcasa de plástico unidas a presión, soldadas o pegadas entre sí alrededor de un conjunto de contactos y pequeñas piezas mecánicas, y los cables emergen a través de orificios o muescas moldeados en el plástico.

Variantes

Existen varias variantes DIP para circuitos integrados, que se distinguen principalmente por el material de embalaje:

- Paquete cerámico dual en línea (CERDIP o CDIP)

- Paquete doble en línea de plástico (PDIP)

- Paquete dual en línea de plástico retráctil (SPDIP) : una versión más densa del PDIP con un paso de cable de 0,07 pulgadas (1,778 mm).

- Paquete en línea dual delgado (SDIP o SPDIP [6] ) : a veces se usa para referirse a un DIP "estrecho" de 0,300 pulgadas (o 300 milésimas de pulgada ) de ancho, normalmente cuando se necesita una aclaración, por ejemplo, para DIP con 24 pines o más, que generalmente vienen en un paquete DIP "ancho" de 0,600 pulgadas de ancho. Un ejemplo de una especificación completa adecuada típica para un paquete DIP "estrecho" sería un ancho de cuerpo de 300 milésimas de pulgada, paso de pines de 0,1 pulgadas (2,54 mm).

Las EPROM se vendían en DIP de cerámica fabricados con una ventana circular de cuarzo transparente sobre el chip para permitir que la parte se borrara con luz ultravioleta . A menudo, los mismos chips también se vendían en paquetes PDIP o CERDIP sin ventanas menos costosos como versiones programables una sola vez (OTP). Los paquetes con y sin ventanas también se usaban para microcontroladores y otros dispositivos que contenían memoria EPROM. Las EPROM con paquete CERDIP con ventana se usaban para la ROM BIOS de muchos de los primeros clones de IBM PC con una etiqueta adhesiva que cubría la ventana para evitar el borrado involuntario por exposición a la luz ambiental.

Los DIP de plástico moldeado tienen un costo mucho menor que los paquetes de cerámica; un estudio de 1979 mostró que un DIP de plástico de 14 pines costaba alrededor de US$0,063 y un paquete de cerámica costaba US$0,82. [7]

Única en línea

Un encapsulado en línea simple ( encapsulado SIP o SIL ) [8] tiene una fila de pines de conexión. No es tan popular como el DIP, pero se ha utilizado para encapsular chips de RAM y múltiples resistencias con un pin común. En comparación con los DIP con un recuento máximo típico de pines de 64, los SIP tienen un recuento máximo típico de pines de 24 con costos de encapsulado más bajos. [9]

Una variante del encapsulado en línea simple utiliza parte del marco conductor para una pestaña disipadora de calor. Este encapsulado de potencia con múltiples conductores es útil para aplicaciones como amplificadores de potencia de audio, por ejemplo.

Cuádruple en línea

El QIP, a veces llamado encapsulado QIL , tiene las mismas dimensiones que un encapsulado DIL, pero los cables de cada lado están doblados en una configuración de zigzag alternada para que quepan cuatro líneas de almohadillas de soldadura (en lugar de dos con un DIL). El diseño QIL aumentó el espacio entre las almohadillas de soldadura sin aumentar el tamaño del encapsulado, por dos razones:

- Permitió una soldadura más confiable . Esto puede parecer extraño hoy en día, dado el espaciado mucho más cercano de los puntos de soldadura que se usa ahora, pero en la década de 1970, el apogeo del QIL, la conexión de puntos de soldadura vecinos en chips DIL era un problema a veces.

- QIL también aumentó la posibilidad de colocar una pista de cobre entre dos puntos de soldadura, lo que resultó muy útil en las PCB de una sola cara y una sola capa, que eran las que entonces eran el estándar.

Recuento y espaciado de cables

Los encapsulados DIP que se encuentran comúnmente y que cumplen con los estándares JEDEC utilizan un espaciado entre conductores (paso de conductores) de 0,1 pulgadas (2,54 mm) (JEDEC MS-001BA). El espaciado entre filas varía según el número de conductores, siendo 0,3 pulgadas (7,62 mm) (JEDEC MS-001) o 0,6 pulgadas (15,24 mm) (JEDEC MS-011) los más comunes. Los espaciamientos entre filas estandarizados menos comunes incluyen 0,4 pulgadas (10,16 mm) (JEDEC MS-010) y 0,9 pulgadas (22,86 mm), así como un espaciado entre filas de 0,3 pulgadas, 0,6 pulgadas o 0,75 pulgadas con un paso de conductores de 0,07 pulgadas (1,778 mm).

La ex Unión Soviética y los países del bloque del Este utilizaban paquetes similares, pero con un espacio entre pines métrico de 2,5 mm en lugar de 0,1 pulgadas (2,54 mm).

El número de cables siempre es par. Para un espaciado de 0,3 pulgadas, los recuentos de cables típicos son 8, 14, 16 y 20; menos comunes son 4, 6, 18, 24 y 28. Para tener un número par de cablesAlgunos DIP tienen cables no conectados (NC) [nb 1] sin usar al chip interno, o están duplicados, por ejemplo, dos pines de tierra. Para un espaciado de 0,6 pulgadas, los recuentos de cables típicos son 24, 28, 32 y 40; menos comunes son 36, 42, 48, 52 y 64 recuentos de cables. Algunos microprocesadores, como el Motorola 68000 y el Zilog Z180 , usaban recuentos de cables tan altos como 64; este es típicamente el número máximo de cables para un encapsulado DIP. [10]

Orientación y numeración de los cables

Como se muestra en el diagrama, los cables están numerados consecutivamente a partir del pin 1. Cuando la muesca de identificación en el paquete está en la parte superior, el pin 1 es la esquina superior izquierda del dispositivo. A veces, el pin 1 se identifica con una marca de pintura o un punto.

Por ejemplo, para un DIP de 14 conductores, con la muesca en la parte superior, los conductores de la izquierda están numerados del 1 al 7 (de arriba a abajo) y la fila derecha de conductores están numerados del 8 al 14 (de abajo a arriba).

En algunos dispositivos DIP (por ejemplo, pantallas LED segmentadas , relés o dispositivos que reemplazan los cables con una aleta disipadora de calor) se omiten los cables . Los cables restantes están numerados como si todas las posiciones tuvieran cables.

Además de permitir la identificación visual humana de la orientación del paquete, la muesca permite que la maquinaria de inserción automática de chips confirme la orientación correcta del chip mediante detección mecánica. [ cita requerida ]

Descendientes

El SOIC (Small Outline IC), un encapsulado de montaje superficial que actualmente es muy popular , particularmente en electrónica de consumo y computadoras personales, es esencialmente una versión reducida del IC PDIP estándar, siendo la diferencia fundamental que lo convierte en un dispositivo SMT una segunda curva en los cables para aplanarlos en paralelo al plano inferior de la carcasa de plástico. El SOJ (Small Outline J-lead) y otros encapsulados SMT con "SOP" (por "Small Outline Package") en sus nombres pueden considerarse parientes adicionales del DIP, su antecesor original. Los encapsulados SOIC tienden a tener la mitad del paso del DIP, y los SOP son la mitad, una cuarta parte del DIP. (0,1"/2,54 mm, 0,05"/1,27 mm y 0,025"/0,635 mm, respectivamente)

Se puede considerar que los encapsulados de matriz de pines (PGA) evolucionaron a partir del DIP. Los PGA con los mismos centros de pines de 0,1 pulgadas (2,54 mm) que la mayoría de los DIP fueron populares para los microprocesadores desde principios y mediados de la década de 1980 hasta la de 1990. Los propietarios de computadoras personales que contienen procesadores Intel 80286 a P5 Pentium pueden estar más familiarizados con estos encapsulados PGA, que a menudo se insertaban en zócalos ZIF en las placas base . La similitud es tal que un zócalo PGA puede ser físicamente compatible con algunos dispositivos DIP, aunque lo inverso rara vez es cierto.

Véase también

- Portador de chip

- Interruptor DIP

- Paquete plano (electrónica)

- Lista de dimensiones de paquetes de circuitos integrados

- NORBIT 2 (un DIP de 19 pines más grande, introducido en 1967)

- Matriz de cuadrícula de pines

- Plan de acción cuantitativa

- Tecnología de montaje superficial

- Paquete en línea en zigzag

Notas

- ^ La abreviatura NC (de "No conectado" o "Sin conexión") también se utiliza para significar " normalmente cerrado " en el contexto de los interruptores. Otra frase utilizada es DNC (de "No conectar").

Referencias

- ^ "véase por ejemplo" (PDF) . Archivado desde el original (PDF) el 2020-09-30 . Consultado el 2010-01-02 .

- ^ Dummer, GWA Invenciones y descubrimientos electrónicos (2.ª ed.), Pergamon Press, ISBN 0-08-022730-9

- ^ Jackson, Kenneth A.; Schröter, Wolfgang Manual de tecnología de semiconductores , John Wiley & Sons, 2000 ISBN 3-527-29835-5 página 610

- ^ Dummer, GWA Invenciones y descubrimientos electrónicos 2.ª ed. Pergamon Press ISBN 0-08-022730-9

- ^ Museo de la Computación recuperado el 16 de abril de 2008

- ^ Por ejemplo, Microchip: http://www.microchip.com/packaging

- ^ Rao R. Tummala, Eugene J. Rymaszewski, Alan G. Klopfenstein Manual de empaquetado de microelectrónica: empaquetado de semiconductores , Springer, 1997 ISBN 0-412-08441-4 página 395

- ^ "Paquete de una sola línea (SIP)". EE Semi . Archivado desde el original el 18 de agosto de 2021.

- ^ Pecht, M. (1994). Pautas de diseño de paquetes de módulos de circuitos integrados, híbridos y multichip. Wiley-IEEE.

- ^ Kang, Sung-Mo; Leblebici, Yusuf (2002). Circuitos integrados digitales CMOS (3.ª ed.). McGraw-Hill. pág. 42. ISBN 0-07-246053-9.

Este artículo incorpora material de dominio público de la Norma Federal 1037C. Administración de Servicios Generales . Archivado desde el original el 22 de enero de 2022.

Este artículo incorpora material de dominio público de la Norma Federal 1037C. Administración de Servicios Generales . Archivado desde el original el 22 de enero de 2022.

Lectura adicional

- Intel (1996). Libro de datos de empaquetado . Mcgraw-Hill. ISBN 1-55512-254-X.OCLC 906673879 .

Enlaces externos

- Documentación, fotografías y vídeos de los paquetes DIP

.jpg/440px-Textoolfassung_28_(smial).jpg)