Temporizador de eventos de alta precisión

Este artículo necesita citas adicionales para su verificación . ( febrero de 2014 ) |

El temporizador de eventos de alta precisión ( HPET ) es un temporizador de hardware disponible en los ordenadores personales modernos compatibles con x86 . En comparación con los tipos de temporizadores más antiguos disponibles en la arquitectura x86, HPET permite un procesamiento más eficiente de aplicaciones altamente sensibles al tiempo, como la reproducción multimedia y el cambio de tareas del sistema operativo . Fue desarrollado conjuntamente por Intel y Microsoft y se ha incorporado a los chipsets de PC desde 2005. Anteriormente denominado por Intel como temporizador multimedia , [1] el término HPET fue seleccionado para evitar confusiones con los temporizadores multimedia de software introducidos en las extensiones multimedia de Windows 3.0 . [2]

Los sistemas operativos más antiguos que no admiten un dispositivo HPET de hardware solo pueden utilizar funciones de temporización más antiguas, como el temporizador de intervalos programable (PIT) o el reloj de tiempo real (RTC). Windows XP , cuando está equipado con la última capa de abstracción de hardware (HAL), también puede utilizar el contador de sello de tiempo (TSC) del procesador o el temporizador de administración de energía ACPI (ACPI PMTIMER), junto con el RTC para proporcionar funciones del sistema operativo que, en versiones posteriores de Windows, proporcionaría el hardware HPET. Resulta confuso que dichos sistemas Windows XP indiquen la conectividad "HPET" en el administrador de controladores de dispositivos, aunque no se esté utilizando el dispositivo Intel HPET.

Características

Un chip HPET consta de un contador ascendente de 64 bits (contador principal) que cuenta a una frecuencia de al menos 10 MHz y un conjunto de comparadores (al menos tres, hasta 256). Estos comparadores tienen un ancho de 32 o 64 bits. El HPET se programa a través de una ventana de E/S mapeada en memoria que se puede descubrir a través de ACPI . El circuito HPET en las PC modernas está integrado en el chip de puente sur . [a]

Cada comparador puede generar una interrupción cuando los bits menos significativos son iguales a los bits correspondientes del valor del contador principal de 64 bits. Los comparadores pueden ponerse en modo de un solo disparo o en modo periódico, con al menos un comparador que admita el modo periódico y todos ellos que admitan el modo de un solo disparo. En el modo de un solo disparo, el comparador dispara una interrupción una vez cuando el contador principal alcanza el valor almacenado en el registro del comparador, mientras que en el modo periódico las interrupciones se generan a intervalos especificados.

Los comparadores pueden ser controlados por el sistema operativo, por ejemplo, para proporcionar un temporizador por CPU para la programación, o por aplicaciones.

Aplicaciones

El HPET puede producir interrupciones periódicas a una resolución mucho mayor que el RTC y se utiliza a menudo para sincronizar transmisiones multimedia, lo que proporciona una reproducción fluida y reduce la necesidad de utilizar otros cálculos de marca de tiempo, como las instrucciones de una CPU basada en x86RDTSC . Esto proporciona una eficiencia mejorada, ya que la CPU no necesita desperdiciar ciclos para compensar la baja resolución de los temporizadores, y permite un uso más agresivo de los estados de suspensión , lo que reduce el consumo de energía. Además de la demanda a nivel de aplicación de un reloj de alta precisión, existen beneficios a nivel de sistema operativo en el programador y a través de la disponibilidad de una base de reloj estable para sistemas multiprocesador . [3]

Comparación con sus predecesores

![[icono]](http://upload.wikimedia.org/wikipedia/commons/thumb/1/1c/Wiki_letter_w_cropped.svg/20px-Wiki_letter_w_cropped.svg.png) | Esta sección necesita ser ampliada con: comparar con temporizador LAPIC, ACPI PM, etc. Puedes ayudar agregando más información. ( Febrero de 2014 ) |

El HPET está pensado para complementar y reemplazar el temporizador de intervalo programable 8254 y la función de interrupción periódica del RTC. En comparación con estos circuitos temporizadores más antiguos, el HPET tiene una frecuencia más alta y contadores de 64 bits más amplios (aunque pueden funcionar en modo de 32 bits). [1]

La especificación HPET no define la frecuencia del temporizador, solo requiere un mínimo de 10 MHz; la frecuencia real es proporcionada al sistema operativo por un registro de hardware que proporciona la cantidad de femtosegundos por período (con un límite superior de100 000 000 fs ). Un valor popular es 14,3 18 MHz, 12 veces la frecuencia estándar 8254 de 1,193 18 MHz.

Aunque el 8254 y el RTC se pueden poner en un modo de un solo disparo similar al HPET, el proceso de configuración es tan lento que su modo de un solo disparo no se utiliza en la práctica para tareas que requieren una programación precisa. [4] En cambio, el 8254 y el RTC se utilizan normalmente en modo periódico con un intervalo de tiempo muy pequeño. Por ejemplo, si una aplicación necesita realizar varias esperas cortas (algunos milisegundos, quizás), es mejor tener un temporizador periódico que funcione constantemente con un período de 1 ms debido al alto costo de configuración de un temporizador de un solo disparo 8254 o RTC. Esto provoca una interrupción en cada milisegundo incluso si la aplicación necesita hacer trabajo real con menos frecuencia. Con HPET, se pueden evitar las interrupciones adicionales, porque el costo de configuración de un temporizador de un solo disparo HPET es considerablemente menor.

Uso y compatibilidad

Los sistemas operativos diseñados antes de que existiera HPET no pueden utilizar HPET, por lo que utilizan otras funciones de temporizador. Los sistemas operativos más nuevos tienden a poder utilizar cualquiera de los dos. Algunos equipos tienen ambos. De hecho, la mayoría de los chips Southbridge actuales tienen instancias compatibles con dispositivos PIT, PIC, APIC ( Advanced Programmable Interrupt Controller ) y RTC incorporados en su silicio, independientemente de que el sistema operativo los utilice o no, lo que ayuda a que las PC muy modernas ejecuten sistemas operativos más antiguos.

Se sabe que los siguientes sistemas operativos no pueden utilizar HPET: Windows XP SP1, [b] y versiones anteriores de Windows , kernels de Linux anteriores a 2.6. [c]

Se sabe que los siguientes sistemas operativos pueden utilizar HPET: Windows XP SP3, [d] Windows Server 2003 SP2 , Windows Server 2008 , Windows Server 2008 R2 , Windows Vista , Windows 7 , versiones basadas en x86 de OS X , sistemas operativos Linux que utilizan el kernel 2.6 (o posterior), FreeBSD [5] y OpenSolaris . [ cita requerida ]

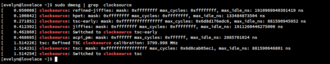

El núcleo de Linux también puede utilizar HPET como fuente de reloj. La documentación de la versión 2 de Red Hat MRG indica que TSC es la fuente de reloj preferida debido a su sobrecarga mucho menor, pero utiliza HPET como alternativa. Una prueba comparativa en ese entorno para 10 millones de recuentos de eventos determinó que TSC tardaba aproximadamente 0,6 segundos, HPET tardaba un poco más de 12 segundos y ACPI Power Management Timer tardaba alrededor de 24 segundos. [6]

En 2019, se decidió incluir en la lista negra HPET en los kernels de Linux más nuevos cuando se ejecuta en algunas CPU Intel ( Coffee Lake ) debido a su inestabilidad. [7]

Problemas

El HPET es un temporizador que funciona continuamente y cuenta hacia arriba, no un dispositivo de un solo disparo que cuenta hacia abajo hasta cero, provoca una interrupción y luego se detiene. Dado que el HPET compara el valor real del temporizador y el valor objetivo programado en términos de igualdad en lugar de "mayor o igual", las interrupciones pueden perderse si el tiempo objetivo ya ha pasado cuando el valor del comparador se escribe en el registro del chip. [8] En tal caso, no solo se pierde la interrupción prevista, sino que en realidad se establece en un futuro lejano (aproximadamente 2 32 o 2 64 conteos). [9] En presencia de interrupciones no enmascarables (como una interrupción de administración del sistema (SMI)) que no tienen un límite superior estricto en su tiempo de ejecución, esta condición de carrera requiere nuevas comprobaciones del temporizador que consumen mucho tiempo después de la configuración y es difícil de evitar por completo. Las dificultades se agravan si el valor del comparador no se sincroniza con el temporizador inmediatamente, sino que se retrasa uno o dos ticks, como hacen algunos chipsets. [8]

Además de mencionar la condición de carrera que se ha comentado anteriormente, un documento de VMware también enumera otras desventajas: "La especificación no exige que el temporizador sea especialmente granular, que tenga poca desviación o que sea rápido de leer. Algunas implementaciones típicas hacen funcionar el contador a unos 18 MHz y requieren aproximadamente la misma cantidad de tiempo (1–2 μs) para leer el HPET que con el temporizador ACPI. Se han observado implementaciones en las que el registro de período tiene un desfase de 800 partes por millón o más". [9]

Notas

- ^ En estos chips altamente integrados, el BIOS a menudo configura el HPET incorrectamente en la ACPI, inicializándolo correctamente solo en modo Intel 8253. Si el ACPI no está configurado correctamente, el SO no puede incluir el HPET en la lista. Y los desarrolladores del BIOS y del SO no ven la necesidad de obtener soporte en tiempo real. Por lo tanto, el HPET solo está allí para satisfacer las necesidades de alta velocidad del sistema. Si el HPET está configurado correctamente en la ACPI desde el BIOS, entonces la página MMIO de ACPI del primer chip HPET debería estar en 0xFED00000 y el segundo HPET en la página 0xFED80000 (consulte la discusión para obtener más información).

- ^ Windows XP SP2 reconoce el temporizador HPET (como un dispositivo con identificador ACPI\PNP0103). Cuando se detecta (por ejemplo, en la placa base Intel DQ45CB), el Administrador de dispositivos (Inicio / Configuración / Panel de control / Sistema / Administrador de dispositivos) muestra el dispositivo "Temporizador de eventos de alta precisión" en la rama "Dispositivos del sistema". Pero este dispositivo no se utiliza en absoluto.

- ^ Con un kernel de Linux , necesita el controlador de dispositivo de reloj de hardware RTC-CMOS más nuevo en lugar del controlador RTC original.

- ^ XP SP3 "emula" la mayor parte de la especificación HPET tal como se redactó en 2002 en previsión de un dispositivo que finalmente hizo su aparición en PCs diseñadas para Windows Vista en 2005. El término "Temporizador de eventos de alta precisión" se utiliza entonces dentro del administrador de controladores para describir los subsistemas de temporización TSC (Time-Stamp-Counter) o ACPI Power Management Timer (PMTimer) incluso cuando no se utiliza el dispositivo Intel HPET de 15 MHz. Si bien es cierto que sólo Windows Vista y versiones posteriores de Windows utilizan el Intel HPET físico de 15 MHz, las características del sistema operativo que se pretendía que cumpliera el HPET ya existían en gran medida en Windows XP, aunque con una especificación diferente (la de 2002 en lugar de la de 2005) y, por lo tanto, con una capacidad reducida. En términos de incorporación física en Windows XP SP3, IRQ0 e IRQ8 se asignan normalmente a un "temporizador de eventos de alta precisión" cuando se utiliza la HAL ACPI (versión 5.1.2600.5512), aunque la llamada a la API QueryPerformanceFrequency devuelve un valor relacionado con la velocidad de reloj nominal del procesador (por ejemplo, 2,6 GHz) o PMTIMER (3,579545 MHz) en lugar del valor especificado por Intel HPET de 15 MHz que obtendría utilizando Windows Vista. Esta anomalía enturbia las aguas sobre lo que se entiende por "HPET" en dichos sistemas, pero claramente no se trata del dispositivo Intel de 15 MHz en esos casos. Tenga en cuenta que esta asignación de IRQ entre comillas "HPET" y la relación de reloj no HPET se pueden encontrar tanto en sistemas Intel como en sistemas AMD, independientemente de que utilicen o no la anulación de arranque /USEPMTIMER. Dado que la especificación original de HPET (en 2002) exige un contador de alta resolución, que luego se expone mediante las llamadas a la API QueryPerformanceFrequency y QueryPerformanceCounter (ya disponibles desde Windows 2000), es QueryPerformanceFrequency la que puede arrojar luz sobre cómo se proporciona realmente este contador de "alta precisión". Un valor alto (en el rango de 1 GHz a 4 GHz) implica que el contador de sello de tiempo (TSC) de la CPU es la fuente. Las primeras CPU multinúcleo de AMD expusieron un problema con las lecturas de QueryPerformanceCounter derivadas de TSC, ya que se verían afectadas por variaciones de velocidad de administración de energía y espectro ensanchado. Si bien esto finalmente se resolvió en diseños de procesadores posteriores al hacer que el reloj de TSC fuera independiente del reloj de la CPU, el temporizador PM en los sistemas ACPI se convirtió en la fuente de contador elegida, lo que requería una anulación de /USEPMTIMER en el archivo BOOT.INI de Windows para imponer su uso. En las máquinas Intel y AMD que utilizan la ACPI HAL junto con el conmutador de arranque /USEPMTIMER, las IRQ 0 y 8 seguirán informando un HPET, pero ahora la frecuencia de rendimiento de consulta informará 3,579545 MHz, que es la frecuencia del PMTIMER. Esto tiene la ventaja expresa de ser independiente de la frecuencia de la CPU y aún proporciona una resolución y precisión de submicrosegundos muy razonables.Irónicamente, las tasas de conteo muy altas obtenidas en los mecanismos TSC (en comparación con PMTIMER o el dispositivo Intel HPET) pueden causar un problema, ya que los intervalos de tiempo medibles son demasiado cortos: existe un límite superior para la utilidad de un contador que se desborda antes de tiempo. También puede ser una molestia que las velocidades de procesador cada vez mayores de los diseños de procesadores más nuevos hagan que este lapso de tiempo utilizable sea aún más corto. Por lo tanto, no es sorprendente que los sistemas PMTIMER e Intel HPET utilicen una tasa fija claramente especificada que está deliberadamente dirigida a producir resoluciones en el rango de submicrosegundos, lo que les permite medir durante períodos más largos de lo que es posible con TSC. Con o sin el conmutador /PMTIMER, la parte de "evento" de la especificación HPET solo se puede emular utilizando otra fuente de temporización, ya que ni una solución TSC subyacente ni una solución PMTIMER incluyen hardware implícito para la activación de eventos aperiódicos como se describe en la especificación, y sin embargo esto está disponible a través de la API de temporizador en Windows XP (con una resolución óptima de 0,9766 ms cuando se utilizan las llamadas API timeBeginPeriod - timeEndPeriod). Esta parte de la especificación aún se cumple mediante el dispositivo RTC con la ayuda del software, a pesar del hecho de que el administrador de dispositivos está citando HPET en las posiciones IRQ0 e IRQ8.

Referencias

- ^ ab Intel Corporation (octubre de 2004), Especificación IA-PC HPET (temporizadores de eventos de alta precisión) (revisión 1.0a) (PDF) , consultado el 15 de junio de 2012

- ^ "Temporizadores multimedia". Microsoft . Consultado el 20 de octubre de 2010 .

- ^ "Especificación IA-PC HPET (temporizadores de eventos de alta precisión)" (PDF) . Intel. Octubre de 2004 . Consultado el 30 de agosto de 2022 .

- ^ Pautas para proporcionar compatibilidad con temporizadores multimedia, 20 de septiembre de 2002 , consultado el 10 de noviembre de 2009

- ^ "Páginas del manual de FreeBSD: hpet(4)". www.freebsd.org .

- ^ "Capítulo 15. Marcas de tiempo". Access.redhat.com. Archivado desde el original el 7 de mayo de 2016. Consultado el 14 de febrero de 2014 .

- ^ "El kernel de Linux desactiva HPET para Intel Coffee Lake". Phoronix .

- ^ de Thomas Gleixner, x86: hpet: Solución a la estupidez del hardware Archivado el 9 de julio de 2012 en archive.today , confirmación fusionada para el kernel de Linux 2.6.36-rc5

- ^ ab Control de tiempo en máquinas virtuales VMware (para VMware vSphere 5.0, Workstation 8.0, Fusion 4.0), página 9