Lógica de tres estados

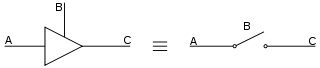

En electrónica digital, un búfer triestado o de tres estados es un tipo de búfer digital que tiene tres estados estables: un estado de salida alta, un estado de salida baja y un estado de alta impedancia . En el estado de alta impedancia, la salida del búfer está desconectada del bus de salida, lo que permite que otros dispositivos controlen el bus sin interferencias del búfer triestado. Esto puede ser útil en situaciones en las que varios dispositivos están conectados al mismo bus y necesitan turnarse para acceder a él. Los sistemas que implementan la lógica de tres estados en su bus se conocen como bus de tres estados o bus triestado .

Los buffers triestado se utilizan comúnmente en sistemas basados en bus, donde varios dispositivos están conectados al mismo bus y necesitan compartirlo. Por ejemplo, en un sistema informático, varios dispositivos, como la CPU, la memoria y los periféricos, pueden estar conectados al mismo bus de datos. Para garantizar que solo un dispositivo pueda transmitir datos en el bus a la vez, cada dispositivo está equipado con un buffer triestado. Cuando un dispositivo desea transmitir datos, activa su buffer triestado, que conecta su salida al bus y le permite transmitir datos. Cuando se completa la transmisión, el dispositivo desactiva su buffer triestado, que desconecta su salida del bus y permite que otro dispositivo acceda al bus.

Los buffers triestado se pueden implementar utilizando puertas, flip-flops u otros circuitos lógicos digitales. Son útiles para reducir la diafonía y el ruido en un bus y para permitir que varios dispositivos compartan el mismo bus sin interferencias.

| APORTE | PRODUCCIÓN | |

|---|---|---|

| A | B | do |

| 0 | 0 | Z (alta impedancia) |

| 1 | Z (alta impedancia) | |

| 0 | 1 | 0 |

| 1 | 1 | |

Usos

El concepto básico del tercer estado, alta impedancia (Hi-Z), es eliminar de manera efectiva la influencia del dispositivo sobre el resto del circuito. Si más de un dispositivo está conectado eléctricamente a otro dispositivo, se suele utilizar poner una salida en el estado Hi-Z para evitar cortocircuitos o que un dispositivo funcione en alto (1 lógico) contra otro dispositivo en bajo (0 lógico).

Los buffers de tres estados también se pueden utilizar para implementar multiplexores eficientes , especialmente aquellos con un gran número de entradas. [1]

Los buffers de tres estados son esenciales para el funcionamiento de un bus electrónico compartido .

La lógica de tres estados puede reducir la cantidad de cables necesarios para controlar un conjunto de LED (multiplexación de tres estados o Charlieplexing ).

Habilitación de salida vs. selección de chip

Muchos dispositivos de memoria diseñados para conectarse a un bus (como chips de RAM y ROM) tienen pines CS ( selección de chip ) y OE (habilitación de salida), que superficialmente parecen hacer lo mismo. Si no se activa CS , las salidas son de alta impedancia.

La diferencia radica en el tiempo necesario para emitir la señal. Cuando se desactiva la selección de chip, el chip no funciona internamente y habrá un retraso significativo entre el suministro de una dirección y la recepción de los datos. (Una ventaja, por supuesto, es que el chip consume una energía mínima en este caso).

Cuando se activa la selección de chip, el chip realiza el acceso internamente y solo se desactivan los controladores de salida finales al desactivar la habilitación de salida. Esto se puede hacer mientras el bus está en uso para otros fines y, cuando finalmente se activa la habilitación de salida, los datos aparecerán con un retraso mínimo. Un chip de ROM o RAM estática con una línea de habilitación de salida generalmente indicará dos tiempos de acceso: uno desde la activación de la selección de chip y la dirección válida, y un segundo tiempo más corto que comienza cuando se activa la habilitación de salida.

Uso de dominadas y pull-downs

Cuando las salidas son triestado (en el estado Hi-Z), se elimina su influencia en el resto del circuito y el nodo del circuito estará "flotando" si ningún otro elemento del circuito determina su estado. Los diseñadores de circuitos suelen utilizar resistencias pull-up o pull-down (normalmente en el rango de 1 a 100 kΩ) para influir en el circuito cuando la salida es triestado.

El bus local PCI proporciona resistencias pull-up, pero se necesitarían varios ciclos de reloj para elevar una señal dada la gran capacidad distribuida del bus . Para permitir el funcionamiento a alta velocidad, el protocolo requiere que cada dispositivo que se conecte al bus eleve las señales de control importantes durante al menos un ciclo de reloj antes de pasar al estado Hi-Z. De esta manera, las resistencias pull-up solo son responsables de mantener las señales del bus frente a la corriente de fuga .

Intel se refiere a esta convención como "tri-estado sostenido" y también la utiliza en el bus de bajo conteo de pines .

Alternativas a un sistema de autobuses de tres estados

La entrada/salida de colector abierto es una alternativa popular a la lógica de tres estados. Por ejemplo, el protocolo de bus I²C (un protocolo de bus de comunicación bidireccional que se usa a menudo entre dispositivos) especifica el uso de resistencias pull-up en las dos líneas de comunicación. Cuando los dispositivos están inactivos, "liberan" las líneas de comunicación y triestadoizan sus salidas, eliminando así su influencia en el circuito. Cuando todos los dispositivos del bus han "liberado" las líneas de comunicación, la única influencia en el circuito son las resistencias pull-up, que elevan las líneas. Cuando un dispositivo quiere comunicarse, sale del estado Hi-Z y hace que la línea baje. Los dispositivos que se comunican mediante este protocolo dejan que la línea flote en alto o la hacen bajar, lo que evita cualquier situación de contención del bus en la que un dispositivo eleva una línea y baja otra.

Los primeros microcontroladores suelen tener algunos pines que solo pueden actuar como entrada, otros pines que solo pueden actuar como salida push-pull y algunos pines que solo pueden actuar como entrada/salida de colector abierto . Un microcontrolador moderno típico tiene muchos pines de entrada/salida de propósito general de tres estados que se pueden programar para actuar como cualquiera de esos tipos de pines.

Un bus de tres estados se utiliza normalmente entre chips en una única placa de circuito impreso (PCB) o, a veces, entre PCB conectadas a una placa base común .

No se recomienda el uso de lógica de tres estados para conexiones dentro del chip, sino para conexiones entre chips. [2]

Los buffers de tres estados, cuando se utilizan para permitir que varios dispositivos se comuniquen en un bus de datos , se pueden reemplazar funcionalmente por un multiplexor . [3] Esto ayudará a seleccionar la salida de un rango de dispositivos y escribir uno en el bus.

Véase también

- Amplificador de búfer

- Nivel lógico

- Metaestabilidad

- Lógica de tres valores

- Lógica de cuatro valores

- Lógica de nueve valores

- No me importa

- Un solo polo, centro desconectado (SPCO)

Notas y referencias

- ^ Hill, Winfield; Horowitz, Paul (1989). El arte de la electrónica. Cambridge University Press. págs. 495–497. ISBN 0-521-37095-7.

- ^ Nota, Buses/redes en chip para SoC "Los buses en chip no utilizan señales triestado porque el bus triestado es difícil para el análisis de tiempos estáticos"

- ^ "Zona de amortiguación de tres estados".

Enlaces externos

- Puertas de salida especial en All About Circuits

- Principio de multiplexación triestado