Serie 5 de Intel

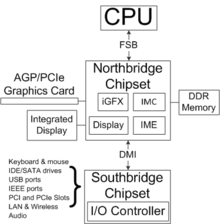

La serie 5 de Intel es una arquitectura informática introducida en 2008 que mejora la eficiencia y equilibra el uso de los canales de comunicación en la placa base . La arquitectura consta principalmente de una unidad central de procesamiento (CPU) (conectada a la tarjeta gráfica y la memoria) y un único chipset (conectado a los componentes de la placa base). Todas las comunicaciones y actividades de la placa base giran en torno a estos dos dispositivos.

La arquitectura es un producto de los ajustes realizados a la serie 4 de Intel para ofrecer placas base de mayor rendimiento manteniendo la eficiencia y el bajo consumo de energía. Los cambios giran en torno al diseño del chipset y del procesador, junto con una reorganización de las funciones y los controladores. El resultado es el primer cambio importante en muchos años de informática.

Concepto de diseño

El concepto de la arquitectura era mejorar la mecánica de la placa base para mantener el ritmo de la CPU a medida que ganaba más velocidad y se multiplicaba en número de núcleos. En la arquitectura anterior, la CPU se comunicaba en gran medida con el componente central de la placa base, el chipset Northbridge , ya que era el intermediario entre la CPU, la memoria y, en la mayoría de los casos, la tarjeta gráfica. La CPU se comunicaba con el chipset Northbridge cuando necesitaba datos de la memoria o cuando necesitaba enviar gráficos a la pantalla. Esta disposición hizo que el canal de comunicación conocido como bus frontal (FSB) se usara mucho. No pasó mucho tiempo hasta que el FSB alcanzara su capacidad máxima o funcionara de manera ineficiente con más núcleos. Con el controlador de memoria y/o el núcleo gráfico trasladados al procesador, se redujo la dependencia de chipsets separados de la placa base para estas funciones.

Pico Ibex

El chipset Ibex Peak incluye solo un concentrador de controlador de plataforma (PCH) por modelo, que proporciona conexiones periféricas y controladores de pantalla para CPU con gráficos integrados a través de la interfaz de pantalla flexible (excluidos los modelos P). Además, el PCH está conectado a la CPU a través de la interfaz de medios directa (DMI).

Aprovechando las CPU Nehalem con gráficos integrados y puertos PCI Express , el Intel Management Engine (ME) y un controlador de pantalla para gráficos integrados, que antes estaban alojados en el puente norte, se trasladan al concentrador de controladores de plataforma (PCH). La función del concentrador de controladores de E/S (ICH) está integrada en el PCH, lo que elimina la necesidad de contar con puentes norte y sur separados .

| Conjunto de chips | Nombre en código | Número de sSpec | Números de piezas | Fecha de lanzamiento | Interfaz de bus | Velocidad de enlace [a] | Carriles PCI Express | PCI | SATA | USB | Apoyo a la IED | TDP |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 3 Gbps | versión 2.0 | |||||||||||

| H55 | Pico Ibex [1] [2] | SLGZX(B3) | BD82H55 (PCH) | Enero de 2010 | DMI | 2 GB/s | 6 PCIe 2.0 a 2,5 GT/s | Sí | 6 puertos | 12 puertos | Sí | 5,2 W |

| P55 | SLH24 (B3), SLGWV (B2) | BD82P55 (PCH) | Septiembre de 2009 | 8 PCIe 2.0 a 2,5 GT/s | 14 puertos | No | 4,7 W | |||||

| H57 | SLGZL(B3) | BD82H57 (PCH) | Enero de 2010 | Sí | 5,2 W | |||||||

| Pregunta 57 | SLGZW(B3) | BD82Q57 (PCH) | 5,1 W |

| Modelo | Marcado superior |

|---|---|

| PM55 Expreso | BD82PM55 |

| Expreso QM57 | BD82QM57 |

| Expreso HM55 | BD82HM55 |

| Expreso HM57 | BD82HM57 |

| Expreso QS57 | BD82QS57 |

| Modelo | Marcado superior | fabuloso | Versión de firmware de ME | PCIe |

|---|---|---|---|---|

| 3400 | BD3400 | 65 nm | 6.0 | 2.0 |

| 3420 | BD3420 | |||

| 3450 | BD3450 |

Tylersburg

La familia de chipsets Tylersburg está destinada a CPU compatibles con Socket LGA 1366 con controladores de memoria de triple canal. A diferencia de los chipsets Ibex Peak , la familia de chipsets Tylersburg no incluye el PCH, y el concentrador de E/S proporciona principalmente puertos PCI Express 2.0 adicionales. Las conexiones periféricas las proporciona el concentrador de controlador de E/S (ICH) conectado a la interfaz DMI. Los IOH de la serie 5 de Intel admiten ICH10, mientras que los IOH de la serie 5500 de Intel admiten ICH9 o ICH10.

Chipset basado en Nehalem de un solo socket

| Conjunto de chips | Nombre en código | Número de sSpec | Números de piezas | Fecha de lanzamiento | Enchufe | Interfaz de bus | Carriles PCI Express | PCI | Compatibilidad con Intel VT-d | SATA | USB | Apoyo a la IED | TDP | ||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 6 Gbps | 3 Gbps | versión 3.0 | versión 2.0 | ||||||||||||

| X58 1 | Tylersburg | SLGBT (B2), SLGMX (B3), SLH3M (C2) | AC82X58 (interfaz de entrada/salida) | Noviembre de 2008 | LGA1366 | Índice de calidad del producto (IPC) | 36× PCIe 2.0 (IOH); 6×PCIe 1.1 (ICH) | Sí | Sí | Ninguno | 6 puertos | Ninguno | 12 puertos | No | 28,6 W2 |

- 1 Nehalem traslada el controlador de memoria al procesador, con lo que el puente norte queda obsoleto . A pesar de ello, LGA 1366 sigue contando con un puente norte y uno sur. El IOH X58 actúa como puente entre el QPI y los periféricos PCI Express y el DMI con el puente sur ICH10/ICH10R .

- 2 X58 TDP incluye el X58 IOH TDP además del ICH10/ICH10R TDP.

Conjuntos de chips Xeon basados en Nehalem de doble zócalo

Los Xeon basados en Nehalem para sistemas de dos conectores, lanzados inicialmente como la serie Xeon 55xx, presentan una estructura de sistema muy diferente: los controladores de memoria están en la CPU y las CPU pueden comunicarse entre sí como pares sin pasar por el chipset. Esto significa que los chipsets 5500 y 5520 (nombre en código inicial Tylersburg-EP) son esencialmente interfaces QPI a PCI Express ; el 5520 está más pensado para estaciones de trabajo gráficas y el 5500 para servidores que no necesitan grandes cantidades de conectividad PCI Express.

| Nombre del lanzamiento | Nombre en clave | Puertos QPI | Velocidad QPI | Entrada/salida rápida | OIC | Otras características | Marcado superior |

|---|---|---|---|---|---|---|---|

| 5500 | Tylersburg-24S, Tylersburg-24D [3] | 1, 2 | 4,8, 5,86 o 6,4 GT/s | 1 ×16 PCIe Gen 2, 2 ×4 PCIe Gen 1 para comunicarse con el puente sur | ICH10 (ICH9 también posible) | Motor de gestión integrado con su propio Ethernet de 100 Mbit [4] | AC5500 SLGMT 901036 (B-3), AC5500 SLH3N 904728 (C-2) |

| 5520 | Tylersburg-36S, Tylersburg-36D | 1, 2 | 4,8, 5,86 o 6,4 GT/s | 2 ×16 PCIe Gen 2, 1 ×4 PCIe Gen 1 para comunicarse con el puente sur | ICH10 (ICH9 también posible) | Motor de gestión integrado con su propio Ethernet de 100 Mbit [4] | AC5520 SLGMU 901037 (B-3), AC5520 SLH3P 904729 (C-2) |

Véase también

Notas

- ^ Velocidad agregada para ambas direcciones

Referencias

- ^ Conjunto de chips Intel serie 5

- ^ Conjunto de chips Intel serie 5 para dispositivos móviles

- ^ "Revisión de la placa base Intel X58 Extreme DX58SO". Guru3D.com . Consultado el 30 de abril de 2023 .

- ^ ab "Chipset Intel® 5520 y chipset Intel® 5500" (PDF) . intel.com . Marzo de 2009 . Consultado el 30 de abril de 2023 .

Enlaces externos

Pico Ibex

- Serie Intel 5: H55, H57, P55, Q57

- Procesadores móviles de la serie Intel 5: HM55, HM57, PM55, QM57, QS57

- Descripción general de los chipsets Intel 3400 y 3420

- Conjunto de chips Intel serie 5 y conjunto de chips Intel serie 3400

- Compatibilidad con el chipset Intel serie 5

- El «pico Ibex» de Intel

Tylersburg

- Conjunto de chips Intel X58 Express

- Serie Intel 5500: 5500, 5520

- Conjunto de chips Intel 5500 y 5520