Interrumpir

Este artículo necesita citas adicionales para su verificación . ( febrero de 2014 ) |

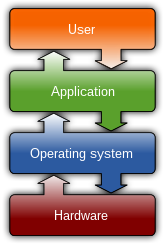

| Sistemas operativos |

|---|

|

| Características comunes |

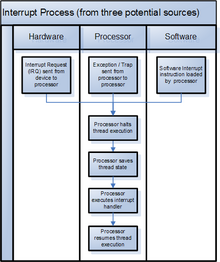

En las computadoras digitales , una interrupción (a veces denominada trampa ) [1] es una solicitud para que el procesador interrumpa el código que se está ejecutando actualmente (cuando está permitido), de modo que el evento pueda procesarse de manera oportuna. Si se acepta la solicitud, el procesador suspenderá sus actividades actuales, guardará su estado y ejecutará una función llamada manejador de interrupciones (o rutina de servicio de interrupciones , ISR) para lidiar con el evento. Esta interrupción suele ser temporal, lo que permite que el software reanude [a] las actividades normales después de que finalice el manejador de interrupciones, aunque la interrupción podría indicar en cambio un error fatal. [2]

Los dispositivos de hardware suelen utilizar interrupciones para indicar cambios de estado físico o electrónico que requieren atención urgente. Las interrupciones también se utilizan habitualmente para implementar la multitarea informática y las llamadas al sistema , especialmente en la informática en tiempo real . Se dice que los sistemas que utilizan interrupciones de estas formas están controlados por interrupciones. [3]

Historia

Las interrupciones de hardware se introdujeron como una optimización, eliminando el tiempo de espera improductivo en los bucles de sondeo , a la espera de eventos externos. El primer sistema que utilizó este enfoque fue el DYSEAC , completado en 1954, aunque los sistemas anteriores proporcionaban funciones de trampa de errores. [4]

El ordenador UNIVAC 1103A es considerado el primero en utilizar interrupciones en 1953. [5] [6] Anteriormente, en el UNIVAC I (1951), "un desbordamiento aritmético activaba la ejecución de una rutina de corrección de dos instrucciones en la dirección 0 o, a elección del programador, hacía que el ordenador se detuviera". El IBM 650 (1954) incorporó la primera aparición de enmascaramiento de interrupciones. El National Bureau of Standards DYSEAC (1954) fue el primero en utilizar interrupciones para E/S. El IBM 704 fue el primero en utilizar interrupciones para depuración , con una "trampa de transferencia", que podía invocar una rutina especial cuando se encontraba una instrucción de bifurcación. El sistema TX-2 del MIT Lincoln Laboratory (1957) fue el primero en proporcionar múltiples niveles de interrupciones de prioridad. [6]

Tipos

Las señales de interrupción pueden emitirse en respuesta a eventos de hardware o software . Se clasifican como interrupciones de hardware o interrupciones de software , respectivamente. Para cualquier procesador en particular, la cantidad de tipos de interrupción está limitada por la arquitectura.

Interrupciones de hardware

Una interrupción de hardware es una condición relacionada con el estado del hardware que puede ser señalizada por un dispositivo de hardware externo, por ejemplo, una línea de solicitud de interrupción (IRQ) en una PC, o detectada por dispositivos integrados en la lógica del procesador (por ejemplo, el temporizador de la CPU en IBM System/370), para comunicar que el dispositivo necesita atención del sistema operativo (OS) [7] o, si no hay SO, del programa de hardware que se ejecuta en la CPU. Dichos dispositivos externos pueden ser parte de la computadora (por ejemplo, controlador de disco ) o pueden ser periféricos externos . Por ejemplo, presionar una tecla del teclado o mover un mouse conectado a un puerto PS/2 desencadena interrupciones de hardware que hacen que el procesador lea la pulsación de la tecla o la posición del mouse.

Las interrupciones de hardware pueden llegar de forma asincrónica con respecto al reloj del procesador y en cualquier momento durante la ejecución de la instrucción. En consecuencia, todas las señales de interrupción de hardware entrantes se condicionan sincronizándolas con el reloj del procesador y se actúa sobre ellas solo en los límites de ejecución de la instrucción.

En muchos sistemas, cada dispositivo está asociado a una señal IRQ específica. Esto permite determinar rápidamente qué dispositivo de hardware solicita servicio y agilizar la reparación de ese dispositivo.

En algunos sistemas más antiguos, como el CDC 3600 de 1964 , [8] todas las interrupciones iban a la misma ubicación y el sistema operativo utilizaba una instrucción especializada para determinar la interrupción desenmascarada pendiente de mayor prioridad. En los sistemas contemporáneos, generalmente hay una rutina de interrupción distinta para cada tipo de interrupción (o para cada fuente de interrupción), a menudo implementada como una o más tablas de vectores de interrupción .

Enmascaramiento

Enmascarar una interrupción es deshabilitarla, de modo que el procesador la posponga [b] o la ignore [c] , mientras que desenmascarar una interrupción es habilitarla. [9 ]

Los procesadores suelen tener un registro interno de máscara de interrupción , [d] que permite habilitar selectivamente [2] (y deshabilitar) las interrupciones de hardware. Cada señal de interrupción está asociada con un bit en el registro de máscara. En algunos sistemas, la interrupción se habilita cuando el bit está configurado y se deshabilita cuando el bit está libre. En otros, ocurre lo contrario y un bit configurado deshabilita la interrupción. Cuando la interrupción está deshabilitada, el procesador puede ignorar la señal de interrupción asociada o puede permanecer pendiente. Las señales que se ven afectadas por la máscara se denominan interrupciones enmascarables .

Algunas señales de interrupción no se ven afectadas por la máscara de interrupción y, por lo tanto, no se pueden desactivar; se denominan interrupciones no enmascarables (NMI). Estas indican eventos de alta prioridad que no se pueden ignorar bajo ninguna circunstancia, como la señal de tiempo de espera de un temporizador de vigilancia . Con respecto a SPARC , la interrupción no enmascarable (NMI), a pesar de tener la prioridad más alta entre las interrupciones, se puede evitar que ocurra mediante el uso de una máscara de interrupción. [10]

Interrupciones faltantes

Un modo de falla es cuando el hardware no genera la interrupción esperada para un cambio de estado, lo que hace que el sistema operativo espere indefinidamente. Según los detalles, la falla puede afectar solo a un proceso o puede tener un impacto global. Algunos sistemas operativos tienen código específicamente para lidiar con esto.

Por ejemplo, IBM Operating System/360 (OS/360) se basa en una interrupción de fin de dispositivo de no listo a listo cuando se ha montado una cinta en una unidad de cinta y no leerá la etiqueta de la cinta hasta que se produzca o simule dicha interrupción. IBM agregó código en OS/360 para que el comando VARY ONLINE simule una interrupción de fin de dispositivo en el dispositivo de destino.

Interrupciones espurias

Una interrupción espuria es una interrupción de hardware para la cual no se puede encontrar una fuente. El término "interrupción fantasma" también se puede utilizar para describir este fenómeno. Las interrupciones espurias tienden a ser un problema con un circuito de interrupción OR cableado conectado a una entrada de procesador sensible al nivel. Dichas interrupciones pueden ser difíciles de identificar cuando un sistema se comporta mal.

En un circuito OR cableado, la carga/descarga de capacitancia parásita a través de la resistencia de polarización de la línea de interrupción provocará una pequeña demora antes de que el procesador reconozca que se ha eliminado la fuente de interrupción. Si el dispositivo de interrupción se elimina demasiado tarde en la rutina de servicio de interrupción (ISR), no habrá tiempo suficiente para que el circuito de interrupción regrese al estado de reposo antes de que finalice la instancia actual de la ISR. El resultado es que el procesador pensará que hay otra interrupción pendiente, ya que el voltaje en su entrada de solicitud de interrupción no será lo suficientemente alto o bajo como para establecer una lógica interna inequívoca de 1 o 0. La interrupción aparente no tendrá una fuente identificable, de ahí el apodo de "espuria".

Una interrupción espuria también puede ser el resultado de anomalías eléctricas debido a un diseño de circuito defectuoso, altos niveles de ruido , diafonía , problemas de sincronización o, más raramente, erratas del dispositivo . [11]

Una interrupción falsa puede provocar un bloqueo del sistema u otra operación indefinida si el ISR no tiene en cuenta la posibilidad de que se produzca dicha interrupción. Como las interrupciones falsas son en su mayoría un problema con los circuitos de interrupción OR cableados, una buena práctica de programación en dichos sistemas es que el ISR compruebe todas las fuentes de interrupción para ver si hay actividad y no realice ninguna acción (excepto posiblemente registrar el evento) si ninguna de las fuentes está interrumpiendo. Incluso pueden provocar el bloqueo del equipo en situaciones adversas.

Interrupciones de software

Una interrupción de software es solicitada por el propio procesador al ejecutar instrucciones específicas o cuando se cumplen ciertas condiciones. Cada señal de interrupción de software está asociada a un controlador de interrupción específico.

Una interrupción de software puede ser causada intencionalmente mediante la ejecución de una instrucción especial que, por diseño, invoca una interrupción cuando se ejecuta. [e] Dichas instrucciones funcionan de manera similar a las llamadas a subrutinas y se utilizan para diversos fines, como solicitar servicios del sistema operativo e interactuar con controladores de dispositivos (por ejemplo, para leer o escribir medios de almacenamiento). Las interrupciones de software también pueden ser activadas por errores de ejecución del programa o por el sistema de memoria virtual .

Por lo general, el núcleo del sistema operativo capturará y manejará dichas interrupciones. Algunas interrupciones se manejan de forma transparente para el programa; por ejemplo, la resolución normal de un fallo de página es hacer que la página requerida sea accesible en la memoria física. Pero en otros casos, como un fallo de segmentación, el sistema operativo ejecuta una devolución de llamada de proceso. En sistemas operativos tipo Unix, esto implica enviar una señal como SIGSEGV , SIGBUS , SIGILL o SIGFPE , que puede llamar a un controlador de señal o ejecutar una acción predeterminada (finalizar el programa). En Windows, la devolución de llamada se realiza utilizando el Manejo de Excepciones Estructurado con un código de excepción como STATUS_ACCESS_VIOLATION o STATUS_INTEGER_DIVIDE_BY_ZERO. [12]

En un proceso del núcleo , suele suceder que algunos tipos de interrupciones de software no deberían ocurrir. Si ocurren, pueden provocar un bloqueo del sistema operativo .

Terminología

Los términos interrupción , trampa , excepción , fallo y aborto se utilizan para distinguir los tipos de interrupciones, aunque "no hay un consenso claro en cuanto al significado exacto de estos términos". [13] El término trampa puede referirse a cualquier interrupción, a cualquier interrupción de software, a cualquier interrupción de software sincrónica o solo a interrupciones causadas por instrucciones con trampa en sus nombres. En algunos usos, el término trampa se refiere específicamente a un punto de interrupción destinado a iniciar un cambio de contexto a un programa de monitorización o depurador . [1] También puede referirse a una interrupción sincrónica causada por una condición excepcional (por ejemplo, división por cero , acceso a memoria no válido , código de operación ilegal ), [13] aunque el término excepción es más común para esto.

x86 divide las interrupciones en interrupciones (de hardware) y excepciones de software , e identifica tres tipos de excepciones: fallos, trampas y abortos. [14] [15] Las interrupciones (de hardware) son interrupciones activadas de forma asincrónica por un dispositivo de E/S y permiten reiniciar el programa sin pérdida de continuidad. [14] Un fallo también se puede reiniciar, pero está vinculado a la ejecución sincrónica de una instrucción: la dirección de retorno apunta a la instrucción que falla. Una trampa es similar a un fallo, excepto que la dirección de retorno apunta a la instrucción que se ejecutará después de la instrucción que produce el fallo; [16] un uso destacado es implementar llamadas al sistema . [15] Un aborto se utiliza para errores graves, como errores de hardware y valores ilegales en las tablas del sistema, y a menudo [f] no permite reiniciar el programa. [16]

Arm utiliza el término excepción para referirse a todos los tipos de interrupciones, [17] y divide las excepciones en interrupciones (de hardware) , abortos , reinicios e instrucciones generadoras de excepciones. Los abortos corresponden a las excepciones x86 y pueden ser abortos de precarga (fallas en la obtención de instrucciones) o abortos de datos (fallas en el acceso a datos), y pueden ser sincrónicos o asincrónicos. Los abortos asincrónicos pueden ser precisos o imprecisos. Los abortos MMU (fallas de página) son sincrónicos. [18]

RISC-V utiliza interrupción como término general y también para el subconjunto externo; las interrupciones internas se denominan excepciones.

Métodos de activación

Cada entrada de señal de interrupción está diseñada para ser activada por un nivel de señal lógica o por un flanco de señal particular (transición de nivel). Las entradas sensibles al nivel solicitan continuamente el servicio del procesador siempre que se aplique un nivel lógico particular (alto o bajo) a la entrada. Las entradas sensibles al flanco reaccionan a los flancos de la señal: un flanco particular (ascendente o descendente) hará que se bloquee una solicitud de servicio; el procesador restablece el bloqueo cuando se ejecuta el controlador de interrupción.

Activado por nivel

Se solicita una interrupción activada por nivel manteniendo la señal de interrupción en su nivel lógico activo particular (alto o bajo) . Un dispositivo invoca una interrupción activada por nivel llevando la señal al nivel activo y manteniéndola en ese nivel. Niega la señal cuando el procesador le ordena que lo haga, generalmente después de que se haya realizado el mantenimiento del dispositivo.

El procesador muestrea la señal de entrada de interrupción durante cada ciclo de instrucción. El procesador reconocerá la solicitud de interrupción si se activa la señal cuando se realiza el muestreo.

Las entradas activadas por nivel permiten que varios dispositivos compartan una señal de interrupción común a través de conexiones OR cableadas. El procesador sondea para determinar qué dispositivos están solicitando servicio. Después de dar servicio a un dispositivo, el procesador puede volver a sondear y, si es necesario, dar servicio a otros dispositivos antes de salir de la ISR.

Activado por borde

Una interrupción activada por flanco es una interrupción señalizada por una transición de nivel en la línea de interrupción, ya sea un flanco descendente (de alto a bajo) o un flanco ascendente (de bajo a alto). Un dispositivo que desea señalar una interrupción envía un pulso a la línea y luego libera la línea a su estado inactivo. Si el pulso es demasiado corto para ser detectado por la E/S sondeada , es posible que se requiera hardware especial para detectarlo. La parte importante de la activación por flanco es que la señal debe realizar la transición para activar la interrupción; por ejemplo, si la señal fuera alta-baja-baja, solo se activaría una interrupción por flanco descendente y el nivel bajo continuo no activaría otra interrupción. La señal debe volver al nivel alto y caer nuevamente para activar otra interrupción. Esto contrasta con una activación por nivel, donde el nivel bajo continuaría creando interrupciones (si están habilitadas) hasta que la señal regrese a su nivel alto.

Las computadoras con interrupciones activadas por flanco pueden incluir un registro de interrupciones que conserva el estado de las interrupciones pendientes. Los sistemas con registros de interrupciones generalmente también tienen registros de máscara de interrupciones.

Respuesta del procesador

El procesador muestrea las señales de activación de interrupciones o el registro de interrupciones durante cada ciclo de instrucción y procesará la interrupción habilitada de mayor prioridad que encuentre. Independientemente del método de activación, el procesador comenzará a procesar la interrupción en el siguiente límite de instrucción después de una activación detectada, lo que garantiza:

- El estado del procesador [g] se guarda de una manera conocida. Normalmente, el estado se almacena en una ubicación conocida, pero en algunos sistemas se almacena en una pila.

- Todas las instrucciones anteriores a la indicada por la PC se han ejecutado completamente.

- No se ha ejecutado ninguna instrucción más allá de la indicada por la PC, o alguna de dichas instrucciones se deshace antes de manejar la interrupción.

- Se conoce el estado de ejecución de la instrucción apuntada por la PC.

Existen varias arquitecturas diferentes para gestionar interrupciones. En algunas, hay un único controlador de interrupciones [19] que debe escanear en busca de la interrupción habilitada con la prioridad más alta. En otras, hay controladores de interrupciones independientes para distintos tipos de interrupciones, [20] canales o dispositivos de E/S independientes, o ambos. [21] [22] Varias causas de interrupción pueden tener el mismo tipo de interrupción y, por lo tanto, el mismo controlador de interrupciones, lo que requiere que el controlador de interrupciones determine la causa. [20]

Implementación del sistema

Las interrupciones pueden ser manejadas completamente en hardware por la CPU, o pueden ser manejadas tanto por la CPU como por otro componente como un controlador de interrupciones programable o un puente sur .

Si se utiliza un componente adicional, dicho componente se conectaría entre el dispositivo de interrupción y el pin de interrupción del procesador para multiplexar varias fuentes de interrupción en una o dos líneas de CPU que normalmente están disponibles. Si se implementa como parte del controlador de memoria , las interrupciones se asignan al espacio de direcciones de memoria del sistema . [ cita requerida ]

En las implementaciones de sistemas en un chip (SoC), las interrupciones provienen de diferentes bloques del chip y generalmente se agregan en un controlador de interrupciones conectado a uno o varios procesadores (en un sistema multinúcleo). [23]

IRQ compartidas

Varios dispositivos pueden compartir una línea de interrupción activada por flanco si están diseñados para ello. La línea de interrupción debe tener una resistencia pull-down o pull-up de modo que, cuando no se active de forma activa, se asiente en su estado inactivo, que es su estado predeterminado. Los dispositivos señalan una interrupción activando brevemente la línea a su estado no predeterminado y dejan que la línea flote (no la activan de forma activa) cuando no están señalando una interrupción. Este tipo de conexión también se conoce como colector abierto . La línea transporta entonces todos los pulsos generados por todos los dispositivos. (Esto es análogo al cordón de tracción de algunos autobuses y trolebuses que cualquier pasajero puede tirar para indicar al conductor que está solicitando una parada). Sin embargo, los pulsos de interrupción de diferentes dispositivos pueden fusionarse si se producen cerca en el tiempo. Para evitar perder interrupciones, la CPU debe disparar en el borde posterior del pulso (por ejemplo, el borde ascendente si la línea se tira hacia arriba y se baja). Después de detectar una interrupción, la CPU debe comprobar todos los dispositivos en busca de requisitos de servicio.

Las interrupciones activadas por flanco no sufren los problemas que tienen las interrupciones activadas por nivel con el uso compartido. El servicio de un dispositivo de baja prioridad se puede posponer arbitrariamente, mientras que las interrupciones de los dispositivos de alta prioridad continúan siendo recibidas y reciben servicio. Si hay un dispositivo al que la CPU no sabe cómo dar servicio, lo que puede generar interrupciones falsas, no interferirá con la señalización de interrupciones de otros dispositivos. Sin embargo, es fácil que se pase por alto una interrupción activada por flanco (por ejemplo, cuando las interrupciones se enmascaran durante un período) y, a menos que haya algún tipo de pestillo de hardware que registre el evento, es imposible recuperarlo. Este problema causó muchos "bloqueos" en el hardware de las primeras computadoras porque el procesador no sabía que se esperaba que hiciera algo. El hardware más moderno a menudo tiene uno o más registros de estado de interrupción que bloquean las solicitudes de interrupciones; un código de manejo de interrupciones controlado por flanco bien escrito puede verificar estos registros para garantizar que no se pase por alto ningún evento.

El bus de la arquitectura estándar de la industria (ISA) utiliza interrupciones activadas por flanco, sin obligar a los dispositivos a compartir líneas IRQ, pero todas las placas base ISA convencionales incluyen resistencias pull-up en sus líneas IRQ, por lo que los dispositivos ISA que se comporten bien y compartan líneas IRQ deberían funcionar bien. El puerto paralelo también utiliza interrupciones activadas por flanco. Muchos dispositivos antiguos asumen que tienen uso exclusivo de líneas IRQ, lo que hace que sea eléctricamente inseguro compartirlas.

Hay tres formas de activar varios dispositivos que "comparten la misma línea". La primera es por conducción exclusiva (conmutación) o conexión exclusiva (a pines). La segunda es por bus (todos conectados a la misma línea de escucha): las tarjetas de un bus deben saber cuándo deben hablar y cuándo no (es decir, el bus ISA). La conversación se puede activar de dos formas: por medio de un pestillo de acumulación o por puertas lógicas. Las puertas lógicas esperan un flujo de datos continuo que se monitorea para detectar señales clave. Los acumuladores solo se activan cuando el lado remoto excita la puerta más allá de un umbral, por lo que no se requiere una velocidad negociada. Cada uno tiene sus ventajas de velocidad versus distancia. Un disparador, en general, es el método en el que se detecta la excitación: borde ascendente, borde descendente, umbral ( el osciloscopio puede activar una amplia variedad de formas y condiciones).

La activación de interrupciones de software debe estar incorporada en el software (tanto en el sistema operativo como en la aplicación). Una aplicación "C" tiene una tabla de activaciones (una tabla de funciones) en su encabezado, que tanto la aplicación como el sistema operativo conocen y usan de manera apropiada, y que no está relacionada con el hardware. Sin embargo, no confunda esto con las interrupciones de hardware que envían señales a la CPU (la CPU ejecuta el software a partir de una tabla de funciones, de manera similar a las interrupciones de software).

Dificultad para compartir líneas de interrupción

Varios dispositivos que comparten una línea de interrupción (de cualquier estilo de activación) actúan como fuentes de interrupción espurias entre sí. Con muchos dispositivos en una línea, la carga de trabajo en el servicio de interrupciones crece en proporción al cuadrado de la cantidad de dispositivos. Por lo tanto, se prefiere distribuir los dispositivos de manera uniforme entre las líneas de interrupción disponibles. La escasez de líneas de interrupción es un problema en los diseños de sistemas más antiguos donde las líneas de interrupción son conductores físicos distintos. Las interrupciones señalizadas por mensaje, donde la línea de interrupción es virtual, se prefieren en las nuevas arquitecturas de sistemas (como PCI Express ) y alivian este problema en gran medida.

Algunos dispositivos con una interfaz de programación mal diseñada no ofrecen ninguna manera de determinar si han solicitado un servicio. Pueden bloquearse o comportarse mal si se les presta servicio cuando no lo desean. Dichos dispositivos no pueden tolerar interrupciones espurias y, por lo tanto, tampoco pueden tolerar compartir una línea de interrupción. Las tarjetas ISA , debido a su diseño y construcción a menudo baratos, son conocidas por este problema. Dichos dispositivos son cada vez más raros, ya que la lógica de hardware se vuelve más barata y las nuevas arquitecturas de sistemas exigen interrupciones compartibles.

Híbrido

Algunos sistemas utilizan una combinación de señalización activada por nivel y por flanco. El hardware no solo busca un flanco, sino que también verifica que la señal de interrupción permanezca activa durante un período de tiempo determinado.

Un uso común de una interrupción híbrida es la entrada NMI (interrupción no enmascarable). Debido a que las NMI generalmente señalan eventos importantes (o incluso catastróficos) del sistema, una buena implementación de esta señal intenta garantizar que la interrupción sea válida verificando que permanezca activa durante un período de tiempo. Este enfoque de dos pasos ayuda a evitar que las interrupciones falsas afecten al sistema.

Mensaje señalado

Una interrupción señalizada por mensaje no utiliza una línea de interrupción física. En su lugar, un dispositivo señala su solicitud de servicio enviando un mensaje corto a través de algún medio de comunicación, normalmente un bus de computadora . El mensaje puede ser de un tipo reservado para interrupciones, o puede ser de algún tipo preexistente, como una escritura en memoria.

Las interrupciones señalizadas por mensaje se comportan de forma muy similar a las interrupciones activadas por flanco, en el sentido de que la interrupción es una señal momentánea en lugar de una condición continua. El software de gestión de interrupciones trata a ambas de forma muy similar. Normalmente, se permite que se fusionen varias interrupciones señalizadas por mensaje pendientes con el mismo mensaje (la misma línea de interrupción virtual), de la misma forma que pueden fusionarse las interrupciones activadas por flanco que estén muy próximas entre sí.

Los vectores de interrupción señalizados por mensaje se pueden compartir en la medida en que se pueda compartir el medio de comunicación subyacente. No se requiere ningún esfuerzo adicional.

Como la identidad de la interrupción se indica mediante un patrón de bits de datos, sin necesidad de un conductor físico independiente, se pueden gestionar de forma eficiente muchas más interrupciones distintas. Esto reduce la necesidad de compartir. Los mensajes de interrupción también se pueden transmitir a través de un bus serial, sin necesidad de líneas adicionales.

PCI Express , un bus de computadora en serie, utiliza exclusivamente interrupciones señalizadas por mensajes .

Timbre de la puerta

En una analogía de pulsar un botón aplicada a los sistemas informáticos , el término timbre o interrupción de timbre se utiliza a menudo para describir un mecanismo mediante el cual un sistema de software puede señalar o notificar a un dispositivo de hardware informático que hay algún trabajo por hacer. Normalmente, el sistema de software colocará datos en algunas ubicaciones de memoria bien conocidas y acordadas mutuamente, y "tocará el timbre" escribiendo en una ubicación de memoria diferente. Esta ubicación de memoria diferente a menudo se denomina región de timbre, e incluso puede haber múltiples timbres que cumplan diferentes propósitos en esta región. Es este acto de escribir en la región de timbre de la memoria lo que "hace sonar el timbre" y notifica al dispositivo de hardware que los datos están listos y esperando. El dispositivo de hardware ahora sabría que los datos son válidos y se puede actuar en consecuencia. Normalmente escribiría los datos en una unidad de disco duro , o los enviaría a través de una red , o los cifraría , etc.

El término interrupción de timbre suele ser un nombre inapropiado . Es similar a una interrupción, porque hace que el dispositivo realice algún trabajo; sin embargo, la región del timbre a veces se implementa como una región sondeada , a veces la región del timbre escribe a través de los registros físicos del dispositivo y, a veces, la región del timbre está conectada directamente a los registros físicos del dispositivo. Al escribir a través de los registros físicos del dispositivo o directamente en ellos, esto puede provocar que se produzca una interrupción real en la unidad central de procesamiento ( CPU ) del dispositivo, si tiene una.

Las interrupciones del timbre se pueden comparar con las interrupciones señalizadas por mensaje , ya que tienen algunas similitudes.

IPI multiprocesador

En sistemas multiprocesador , un procesador puede enviar una solicitud de interrupción a otro procesador a través de interrupciones entre procesadores [h] (IPI).

Actuación

Las interrupciones ofrecen una sobrecarga baja y una buena latencia con poca carga, pero se degradan significativamente con una tasa de interrupciones alta a menos que se tomen precauciones para evitar varias patologías. El fenómeno en el que el rendimiento general del sistema se ve gravemente afectado por una cantidad excesiva de tiempo de procesamiento dedicado a gestionar interrupciones se denomina tormenta de interrupciones .

Existen diversas formas de bloqueos activos , cuando el sistema pasa todo su tiempo procesando interrupciones y excluyendo otras tareas requeridas. En condiciones extremas, una gran cantidad de interrupciones (como un tráfico de red muy alto) puede bloquear por completo el sistema. Para evitar tales problemas, un sistema operativo debe programar el manejo de las interrupciones de red con el mismo cuidado con el que programa la ejecución de procesos. [24]

Con procesadores multinúcleo, se pueden lograr mejoras de rendimiento adicionales en el manejo de interrupciones a través del escalamiento del lado de recepción (RSS) cuando se utilizan NIC de cola múltiple . Estas NIC proporcionan múltiples colas de recepción asociadas a interrupciones separadas; al enrutar cada una de esas interrupciones a diferentes núcleos, el procesamiento de las solicitudes de interrupción activadas por el tráfico de red recibido por una única NIC se puede distribuir entre múltiples núcleos. La distribución de las interrupciones entre los núcleos se puede realizar automáticamente por el sistema operativo, o el enrutamiento de las interrupciones (generalmente denominado afinidad IRQ ) se puede configurar manualmente. [25] [26]

Una implementación basada puramente en software de la distribución del tráfico de recepción, conocida como direccionamiento de paquetes de recepción (RPS), distribuye el tráfico recibido entre los núcleos que se encuentran más adelante en la ruta de datos, como parte de la funcionalidad del controlador de interrupciones . Las ventajas de RPS sobre RSS incluyen la ausencia de requisitos de hardware específico, filtros de distribución de tráfico más avanzados y una tasa reducida de interrupciones producidas por una NIC. Como desventaja, RPS aumenta la tasa de interrupciones entre procesadores (IPI). El direccionamiento de flujo de recepción (RFS) lleva el enfoque basado en software más allá al tener en cuenta la localidad de la aplicación ; se logran mejoras adicionales en el rendimiento al procesar las solicitudes de interrupción por los mismos núcleos en los que la aplicación de destino consumirá paquetes de red particulares. [25] [27] [28]

Usos típicos

Las interrupciones se utilizan comúnmente para dar servicio a temporizadores de hardware, transferir datos hacia y desde el almacenamiento (por ejemplo, E/S de disco) e interfaces de comunicación (por ejemplo, UART , Ethernet ), manejar eventos del teclado y del mouse, y para responder a cualquier otro evento sensible al tiempo según lo requiera el sistema de la aplicación. Las interrupciones no enmascarables se utilizan típicamente para responder a solicitudes de alta prioridad, como tiempos de espera de temporizadores de vigilancia, señales de apagado y trampas .

Los temporizadores de hardware se utilizan a menudo para generar interrupciones periódicas. En algunas aplicaciones, el controlador de interrupciones cuenta dichas interrupciones para realizar un seguimiento del tiempo absoluto o transcurrido, o las utiliza el programador de tareas del sistema operativo para gestionar la ejecución de los procesos en ejecución , o ambas cosas. Las interrupciones periódicas también se utilizan habitualmente para invocar el muestreo de dispositivos de entrada, como convertidores analógicos a digitales , interfaces de codificadores incrementales y entradas GPIO , y para programar dispositivos de salida, como convertidores digitales a analógicos , controladores de motores y salidas GPIO.

Una interrupción de disco señala la finalización de una transferencia de datos desde o hacia el periférico de disco; esto puede hacer que se ejecute un proceso que está esperando para leer o escribir. Una interrupción de apagado predice una pérdida inminente de energía, lo que permite que la computadora realice un apagado ordenado mientras aún queda suficiente energía para hacerlo. Las interrupciones del teclado generalmente hacen que las pulsaciones de teclas se almacenen en búfer para implementar la escritura anticipada .

Las interrupciones se utilizan a veces para emular instrucciones que no están implementadas en algunas computadoras de una familia de productos. [29] [30] Por ejemplo, las instrucciones de punto flotante pueden implementarse en hardware en algunos sistemas y emularse en sistemas de menor costo. En el último caso, la ejecución de una instrucción de punto flotante no implementada causará una interrupción de excepción de "instrucción ilegal". El controlador de interrupciones implementará la función de punto flotante en el software y luego regresará al programa interrumpido como si la instrucción implementada en hardware se hubiera ejecutado. [31] Esto proporciona portabilidad del software de aplicación en toda la línea.

Las interrupciones son similares a las señales , con la diferencia de que las señales se utilizan para la comunicación entre procesos (IPC), mediadas por el núcleo (posiblemente a través de llamadas al sistema) y manejadas por los procesos, mientras que las interrupciones son mediadas por el procesador y manejadas por el núcleo . El núcleo puede pasar una interrupción como señal al proceso que la causó (los ejemplos típicos son SIGSEGV , SIGBUS , SIGILL y SIGFPE ).

Véase también

- Controlador de interrupciones programable avanzado (APIC)

- Llamada de interrupción del BIOS

- Programación basada en eventos

- Manejo de excepciones

- INT (instrucción x86)

- Interrumpir la coalescencia

- Manejador de interrupciones

- Latencia de interrupción

- Interrupciones en procesadores 65xx

- Lista de interrupciones de Ralf Brown

- Interrupciones en la arquitectura IBM System/360

- Sistema activado por tiempo

- Funcionamiento periférico autónomo

Notas

- ^ El sistema operativo podría reanudar el proceso interrumpido o podría cambiar a un proceso diferente.

- ^ Normalmente, los eventos de interrupción asociados con E/S permanecen pendientes hasta que la interrupción se habilita o se borra explícitamente, por ejemplo, mediante la instrucción de interrupción pendiente de prueba ( TPI ) de IBM System/370-XA y posteriores.

- ^ Por ejemplo, cuando los bits de máscara de programa en el IBM System/360 son 0 (deshabilitados), los eventos de desbordamiento y significancia correspondientes no dan como resultado una interrupción pendiente.

- ^ El registro de máscara puede ser un solo registro o varios registros, por ejemplo, bits en el PSW y otros bits en registros de control .

- ^ Ver INT (instrucción x86)

- ^ Algunos sistemas operativos pueden recuperarse de errores graves, por ejemplo, la paginación de una página desde un archivo de paginación después de un error ECC incorregible en una página no alterada.

- ^ Esto podría ser solo el contador de programa (PC) , un PSW o varios registros.

- ^ Conocidos como toques de hombro en algunos sistemas operativos de IBM.

Referencias

- ^ ab "The Jargon File, versión 4.4.7". 27 de octubre de 2003. Consultado el 20 de enero de 2022 .

- ^ ab Jonathan Corbet; Alessandro Rubini; Greg Kroah-Hartman (2005). "Linux Device Drivers, Third Edition, Chapter 10. Interrupt Handling" (PDF) . O'Reilly Media . p. 269. Consultado el 25 de diciembre de 2014. Luego, solo es cuestión de limpiar, ejecutar interrupciones de software y volver al trabajo normal .

Es posible que el "trabajo normal" haya cambiado como resultado de una interrupción (el controlador podría ser

un proceso, por ejemplo), por lo que lo último que sucede al regresar de una interrupción es una posible reprogramación del procesador.

wake_up - ^ Rosenthal, Scott (mayo de 1995). "Conceptos básicos de las interrupciones". Archivado desde el original el 26 de abril de 2016. Consultado el 11 de noviembre de 2010 .

- ^ Codd, Edgar F. "Multiprogramación". Avances en computadoras . 3 : 82.

- ^ Bell, C. Gordon; Newell, Allen (1971). Estructuras informáticas: lecturas y ejemplos. McGraw-Hill. pág. 46. ISBN 9780070043572. Recuperado el 18 de febrero de 2019 .

- ^ de Smotherman, Mark. "Interrupts" . Consultado el 22 de diciembre de 2021 .

- ^ "Interrupciones de hardware" . Consultado el 9 de febrero de 2014 .

- ^ "Instrucciones de interrupción". Manual de referencia del sistema informático Control Data 3600 (PDF) . Control Data Corporation. Julio de 1964. págs. 4–6. 60021300.

- ^ Bai, Ying (2017). Ingeniería de microcontroladores con MSP432: fundamentos y aplicaciones. CRC Press. p. 21. ISBN 978-1-4987-7298-3. LCCN 2016020120.

En el sistema Cortex-M4, las interrupciones y excepciones tienen las siguientes propiedades: ... Generalmente, se utiliza un solo bit en un registro de máscara para enmascarar (deshabilitar) o desenmascarar (habilitar) la ocurrencia de ciertas interrupciones/excepciones.

- ^ "Niveles de interrupción" . Consultado el 17 de noviembre de 2023 .

- ^ Li, Qing; Yao, Caroline (2003). Conceptos de tiempo real para sistemas integrados . CRC Press. pág. 163. ISBN 1482280825.

- ^ "Excepciones de hardware". docs.microsoft.com . 3 de agosto de 2021.

- ^ ab Hyde, Randall (1996). "Capítulo diecisiete: interrupciones, trampas y excepciones (parte 1)". El arte de la programación en lenguaje ensamblador . Consultado el 22 de diciembre de 2021 .

El concepto de interrupción es algo que se ha ampliado en alcance a lo largo de los años. La familia 80x86 solo ha aumentado la confusión en torno a las interrupciones al introducir la instrucción int (interrupción de software). De hecho, diferentes fabricantes han utilizado términos como excepciones, fallos, abortos, trampas e interrupciones para describir los fenómenos que analiza este capítulo. Lamentablemente, no existe un consenso claro en cuanto al significado exacto de estos términos. Diferentes autores adoptan diferentes términos para su propio uso.

- ^ ab "Manual del desarrollador de software de arquitecturas Intel® 64 e IA-32, volumen 1: arquitectura básica". pp. 6–12 Vol. 1 . Consultado el 22 de diciembre de 2021 .

- ^ ab Bryant, Randal E.; O'Hallaron, David R. (2016). "8.1.2 Clases de excepciones". Sistemas informáticos: la perspectiva de un programador (tercera edición global). Harlow: Pearson. ISBN 978-1-292-10176-7.

- ^ ab "Manual del desarrollador de software de arquitecturas Intel® 64 e IA-32, volumen 3A: Guía de programación del sistema, parte 1". pág. 6-5 Vol. 3A . Consultado el 22 de diciembre de 2021 .

- ^ "Manejo de excepciones". developer.arm.com . Guía del programador de la serie ARM Cortex-A para ARMv7-A . Consultado el 21 de enero de 2022 .

- ^ "Tipos de excepción". developer.arm.com . Guía del programador de la serie ARM Cortex-A para ARMv7-A . Consultado el 22 de diciembre de 2021 .

- ^ Control Data 6400/6500/6600 Computer Systems Reference Manual (PDF) . Revisión K. Control Data Corporation . 11 de octubre de 1966. 60021300K . Consultado el 17 de mayo de 2023 .

- ^ ab IBM System/360 Principles of Operation (PDF) (Octava ed.). IBM . Septiembre de 1968. pág. 77. A22-6821-7.

- ^ Manual del procesador PDP-11 PDP11/04//34a/44/60/70 (PDF) . Digital Equipment Corporation . 1979. págs. 128–131.

- ^ Manual de interfaz y periféricos PDP-11 (PDF) . Digital Equipment Corporation . pág. 4.

- ^ Yiu, Joseph (1 de enero de 2010), Yiu, Joseph (ed.), "CAPÍTULO 2: Descripción general del Cortex-M3", La guía definitiva del ARM Cortex-M3 (segunda edición) , Oxford: Newnes, págs. 11-24, doi : 10.1016/b978-1-85617-963-8.00005-3, ISBN 978-1-85617-963-8, consultado el 11 de octubre de 2023

- ^ Mogul, Jeffrey C.; Ramakrishnan, KK (1997). "Eliminación del bloqueo activo de recepción en un núcleo controlado por interrupciones". ACM Transactions on Computer Systems . 15 (3): 217–252. doi :10.1145/263326.263335. S2CID 215749380 . Consultado el 11 de noviembre de 2010 .

- ^ ab Tom Herbert; Willem de Bruijn (9 de mayo de 2014). "Documentación/redes/scaling.txt". Documentación del núcleo de Linux . kernel.org . Consultado el 16 de noviembre de 2014 .

- ^ "Hoja de datos de la familia de controladores Ethernet Gigabit Intel 82574" (PDF) . Intel . Junio de 2014. p. 1 . Consultado el 16 de noviembre de 2014 .

- ^ Jonathan Corbet (17 de noviembre de 2009). «Recepción de paquetes». LWN.net . Consultado el 16 de noviembre de 2014 .

- ^ Jake Edge (7 de abril de 2010). «Receive flow steering» (Dirección del flujo de recepción). LWN.net . Consultado el 16 de noviembre de 2014 .

- ^ "SIMULADOR DE DECIMAL" (PDF) . Sistema operativo IBM System/360: guía para la compatibilidad con el modelo 91 (PDF) . Biblioteca de referencia de sistemas. págs. 11–12. C28-6666-0 . Consultado el 2 de septiembre de 2024 .

- ^ Thusoo, Shalesh; et al. "Patente US 5632028 A". Google Patents . Consultado el 13 de agosto de 2017 .

- ^ Altera Corporation (2009). Referencia del procesador Nios II (PDF) . pág. 4. Consultado el 13 de agosto de 2017 .

Enlaces externos

- Las interrupciones se hacen fáciles

- Interrupciones para el microcontrolador PIC de Microchip

- Tabla de interrupciones de IBM PC

- Notas sobre interrupciones de computación concreta de la asignatura CMPUT 296 de la Universidad de Alberta, archivadas desde el original el 13 de marzo de 2012

- Interrupciones en el cambio de pin de Arduino: artículo de Adityapratap Singh