Estancamiento del oleoducto

Este artículo necesita citas adicionales para su verificación . ( agosto de 2012 ) |

En el diseño de procesadores informáticos canalizados , un bloqueo en la canalización es un retraso en la ejecución de una instrucción para resolver un peligro . [1]

Detalles

En una secuencia estándar de cinco etapas , durante la etapa de decodificación , la unidad de control determinará si la instrucción decodificada se lee desde un registro en el que se escribe la instrucción que se está ejecutando actualmente. Si se cumple esta condición, la unidad de control detendrá la instrucción durante un ciclo de reloj. También detiene la instrucción en la etapa de búsqueda, para evitar que la instrucción en esa etapa sea sobrescrita por la siguiente instrucción en el programa. [2]

En una arquitectura de Von Neumann que utiliza el registro del contador de programa (PC) para determinar la instrucción actual que se está recuperando en la tubería, para evitar que se obtengan nuevas instrucciones cuando una instrucción en la etapa de decodificación se ha estancado, el valor en el registro PC y la instrucción en la etapa de recuperación se conservan para evitar cambios. Los valores se conservan hasta que la instrucción que causa el conflicto haya pasado por la etapa de ejecución. [3] Este tipo de evento a menudo se denomina burbuja , por analogía con una burbuja de aire en una tubería de fluido.

En algunas arquitecturas, la etapa de ejecución de la canalización debe estar siempre realizando una acción en cada ciclo. En ese caso, la burbuja se implementa enviando instrucciones NOP ("sin operación") a la etapa de ejecución, hasta que la burbuja se vacía.

Ejemplos

Cronología

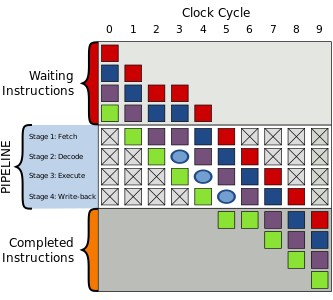

Lo que sigue son dos ejecuciones de las mismas cuatro instrucciones a través de una cadena de procesamiento de 4 etapas pero, por alguna razón, una demora en la obtención de la instrucción púrpura en el ciclo n.° 2 hace que se cree una burbuja que también retrasa todas las instrucciones posteriores.

|  |

| Ejecución normal | Ejecución con burbuja |

Canalización RISC clásica

El siguiente ejemplo muestra una burbuja que se inserta en una secuencia de comandos RISC clásica , con cinco etapas (IF = obtención de instrucción, ID = decodificación de instrucción, EX = ejecución, MEM = acceso a memoria, WB = escritura de registro). En este ejemplo, los datos disponibles después de la etapa MEM (cuarta etapa) de la primera instrucción se requieren como entrada para la etapa EX (tercera etapa) de la segunda instrucción. Sin una burbuja, la etapa EX (tercera etapa) solo tiene acceso a la salida de la etapa EX anterior. Por lo tanto, agregar una burbuja resuelve la dependencia del tiempo sin necesidad de propagar los datos hacia atrás en el tiempo (lo cual es imposible).

| Pasando atrás en el tiempo | Problema resuelto usando una burbuja |

|  |

Véase también

Referencias

- ^ Patterson, David A.; Hennessy, John L., Organización y diseño de computadoras (4.ª ed.), Morgan Kaufmann , pág. 338

- ^ Patterson, David A; Hennessy, John L (2014), Organización y diseño de computadoras: la interfaz hardware/software (5.ª ed.), pág. 318, OCLC 1130276006 , consultado el 25 de mayo de 2020

- ^ Patterson, David A.; Hennessy, John L., Organización y diseño de computadoras (4.ª ed.), Morgan Kaufmann , pág. 373